基于FPGA的直接數字頻率合成技術設計

2 DDS在FPGA中的實現

考慮到本系統的規模以及以后的擴展需要,該系統中的DDS電路采用VHDL硬件描述語言來實現,因為VHDL語言設計的電路模塊可以方便地移植到不同的FPGA芯片中。由于硬件原因,本系統的最高頻率為100kHz,因此,采用常規設計即可滿足要求,但若要應用于高速系統,還要采用一些提高系統運行速度的措施,如采用流水線技術,即在設計中把延時較大的組合邏輯塊切割成兩塊大致相等的組合邏輯塊,并在這兩個邏輯塊中插入觸發器,也可通過多個觸發器時鐘來提高系統速度,還可以采用ALTREA 公司的FPGA器件所特有的進位鏈來設計高速電路。

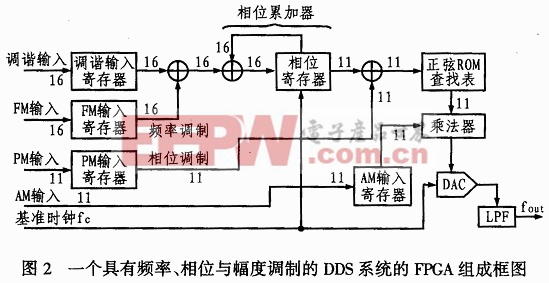

圖2所示為一個具有頻率、相位與幅度調制的DDS系統的FPGA組成框圖。它的頻率調制可以在調諧寄存器與相位累加器之間插入一加法器來實現,頻率調制與相位調制有相同的分辨率,因此,頻率可以覆蓋整個調諧頻段。相位調制器可通過在相位累加器后插入一個加法器來實現。幅度調制則是在正弦查找表后插入一個乘法器來實現。該系統具有高精度、高穩定性等特點。

2.1 ROM查找表的設計

ROM查找表在整個設計中是一個比較重要的部分。為了保證波形的平滑,設計時可將一個周期分為1024個點。但是,點數太多時,用文本方式輸入可能有很多困難。因此,應當用C語言描述正弦方程式,最后再將其轉化為所需的mif文件。以下是其C語言的源程序:

main()

{int i;float s;

for(i=0;i<1024;i++)

{ s = sin(atan(1)*8*i/1024);

......

2.2 DDS主模塊設計

DDS主模塊部分可根據上述原理,采用VHDL來描述,以下是部分源程序:

BEGIN

PROCESS (clk)

BEGIN

IF(clk'event AND clk='1') THEN

\\時鐘上升沿觸發

freqw<=freqin;

acc<=acc+freqw; \\開始累加

END IF;

END PROCESS;

romaddr<=acc(adder width-1 downto adder width-10); \\累加結果的高11位作為

查找表的地址位

i_rom:lpm_rom \\調用ROM查找表

......

評論