基于FPGA的直接數字頻率合成技術設計

直接數字頻率合成(DirectDigital FraquencySyn-thesis即DDFS,一般簡稱DDS)是從相位概念出發直接合成所需波形的一種新的頻率合成技術。它在相對帶寬、頻率轉換時間、相位連續性、正交輸出、高分辨率以及集成化等一系列性能指標方面已遠遠超過了傳統頻率合成技術。當累加器的N很大時,最低輸出頻率可達Hz、mHz甚至μHz。也就是說:DDS的最低合成頻率接近于零頻。如果fc為50MHz, 那么當N為48位時,其分辨率可達179nHz。轉換時間最快可達10ns的量級,這都是傳統頻率合成所不能比擬的。但它的不足之處是最高工作頻率會受限、噪聲和雜波不夠理想。

本文引用地址:http://www.104case.com/article/191944.htm本設計采用ALTERA公司的FPGA芯片EP1K30TC-144來實現DDS技術。EP1K30芯片屬ALTERA公司的ACEX系列,該系列是ALTERA公司著眼于通信、音頻處理及類似場合應用而推出的FPGA器件系列芯片,它采用0.22/0.18微米混合工藝,密度從10000門到100000門。所有ACEX系列器件均兼容64bit、66MHz的PCI,并支持鎖相環電路。ACEX1K采用查找表(LUT)和EAB(嵌入式陣列塊)相結合的結構,可用來實現存儲器、專用邏輯功能和通用邏輯功能,每個EBA能提供4096比特的存儲空間,每個LE包含4個輸入LUT、一個可編程的觸發器、進位鏈和一個層疊鏈。合理運用進位鏈能夠提高系統運行速度。

EP1K30TC-144的最大系統門數為119000,它有1728個邏輯宏單元數和5個嵌入式陣列塊,最大可提供2kB的ROM/RAM位,因而可完全滿足DDS設計的要求。

1 DDS的實現過程

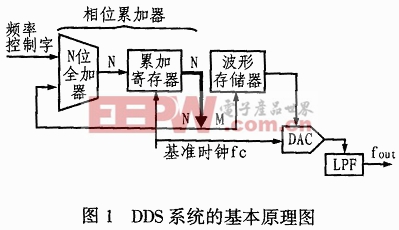

圖1為DDS系統的基本原理圖,圖中的相位累加器由N位全加器和N位累加寄存器級聯而成,可對頻率控制字的2進制碼進行累加運算,是典型的反饋電路,產生的累加結果的高M位作為ROM查找表的取樣地址值,而此查找表中儲存了一個周期的正弦波幅度值。顯然,此處存儲器ROM可以看作一個從相位到正弦幅值的轉換器。這樣,用ROM的輸出值來驅動DAC,然后經濾波即可轉換成所需要的模擬正弦波形;同時N位累加輸出又可作為全加器的下一輪數據與頻率數據相加,直到相位累加器加滿產生溢出,從而完成一個周期,也就是DDS信號的頻率周期。

評論