基于FPGA的改進型分組交織器的設計與實現

2.4 讀寫使能控制設計

考慮到雙端口RAM對其內部同一單元地址不能同時進行讀寫操作,因此,整個交織器設計需用讀寫使能控制電路用來對雙端口RAM的地址讀寫進行控制,并同時決定讀寫發生器何時開始工作。由于雙端口RAM的讀、寫實現都是從零地址開始的,因而RAM內的每個存儲單元的讀操作都應在寫操作之后,從而保證每個讀出數據的有效性。

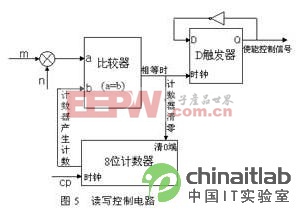

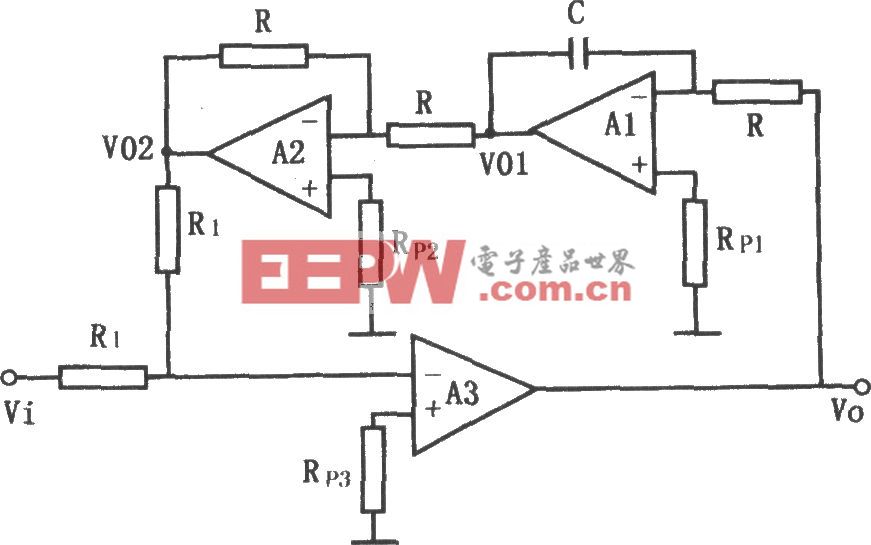

讀寫使能控制電路如圖5所示,讀寫控制電路采用類似于分頻器原理[4]的工作方式,電路主要由計數器、比較器和D觸發器來實現:計數器與n m比較的結果作為D觸發器的時鐘脈沖信號,當計數器的計數值等于n m時,觸發器的輸出狀態進行一次反轉,即相當于構成了一個n m的分頻器電路。觸發器的輸出結果分成兩路:一路送到雙端口RAM的寫地址使能端;另一路經過反相后送給讀地址使能端。這樣便可以使存儲器RAM在“n m”的地址空間范圍內交替進行“讀/寫”數據的操作。

讀寫使能控制電路

2.5 設計中的遇到的問題及解決辦法

交織器的設計中包含的運算有相乘和相加,相乘會造成字長的變化。這便會帶來數據位數匹配的問題,下面我們以讀地址電路(圖4)為例給出解決辦法:

進入乘法器的兩路數據均為8位,經過乘法運算后,數據位數會增加到16位,同時需要與來自計數器Ⅱ的8位數據進行加法運算。通常情況下多采取舍入或截尾的方法,即將16位數據的高8位字節舍去,這種方法的不足是當m、n的乘積大于256(11111111H)時,數據的高8位不全為0,舍去會帶來輸出結果的錯誤,因而可能造成交織器輸出碼字的錯誤。因此,可采用“補位”的辦法,將輸入加法器的8位數據補成16位(在8位數據前補8位0),以增長位寬從而達到數位匹配的目的。

3 QuartusⅡ仿真結果及分析

交織器的仿真波形如圖6所示(其中“clk”為驅動時鐘,“rden”、“wren”為讀、寫使能,“data”、“result”為輸入、輸出雙端口RAM的數據序列):

Quartus

從QuartusⅡ波形仿真結果看到當交織矩陣的m,n值為5和3時,雙口RAM的輸出數據為“0、5、10、1、6…”;當m,n調整為8和 6后,雙口RAM的輸出為“0、8、16、24…”。可以看出,在任意選取不同的m值和n值后,交織器能夠根據分組交織的原理將輸入RAM的數據字或比特位流進行交織,輸出所需的數據序列,達到了交織矩陣深度和寬度可控的目的。

4 小結

本文介紹了可針對不同交織需要的改進型分組交織器FPGA設計,該交織器的主要特點是可根據信道中突發誤碼的長度、出現的頻率以及糾錯碼的約束長度、糾錯能力設定合適的交織深度和寬度(m,n),需要指出的是,m,n選得越大,信道編碼的約束長度越大,從而對付信道中長突發差錯的能力也就越強,但m,n選得越大,也就需要越大的存儲空間,同時會引入更長的延時,所以應根據數字通信系統的實際情況選擇合適的m值和n值。

本文作者創新點:對傳統分組交織器進行了改進,實現了分組交織器的交織矩陣深度和寬度可控,能夠很好的滿足不同數據幀傳輸的要求,具有更好的抗信道突發錯誤的能力。

評論