基于FPGA的改進(jìn)型分組交織器的設(shè)計(jì)與實(shí)現(xiàn)

在整個(gè)循環(huán)過程中,讀地址變量add不斷輸出“亂序”的交織地址add=j n+i,以達(dá)到設(shè)計(jì)的要求。

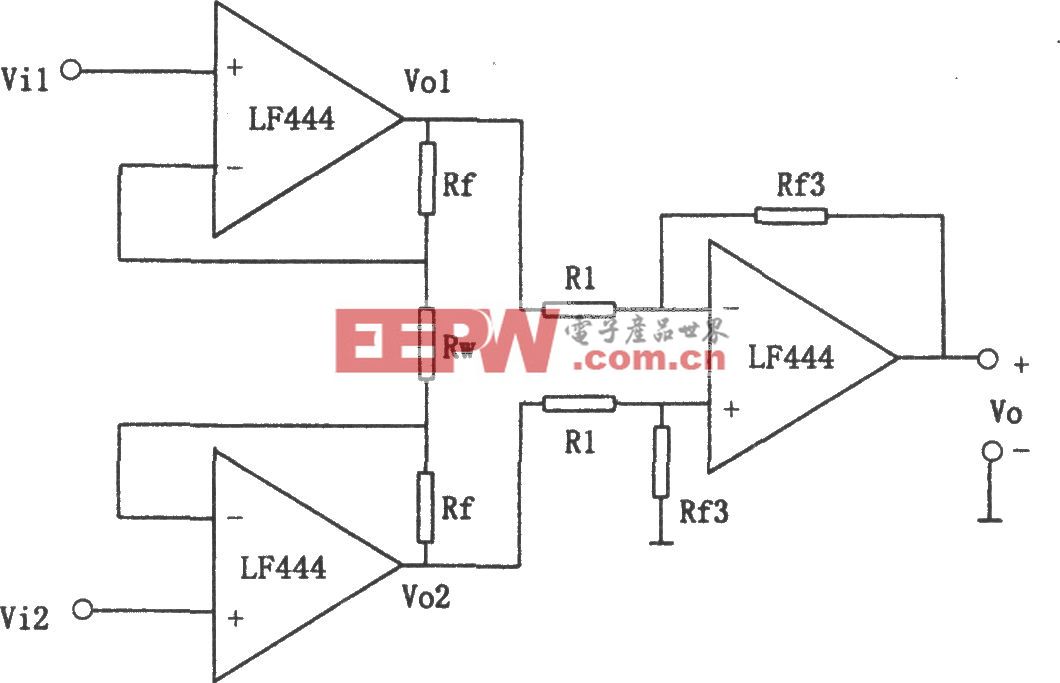

通過上述分析可以看出,算法中運(yùn)用了加法、乘法、比較、計(jì)數(shù)等算術(shù)邏輯運(yùn)算,則地址生成的FPGA設(shè)計(jì)過程中,需要運(yùn)用加法器,乘法器,比較器,計(jì)數(shù)器等器件以實(shí)現(xiàn)相應(yīng)功能。在設(shè)計(jì)過程中,這些器件采用由QuartusⅡ軟件為設(shè)計(jì)人員提供的參數(shù)化宏單元模塊LPM(library of parameterized modules),使用它不僅可以簡化電路復(fù)雜度,而且大大提高了設(shè)計(jì)速度。

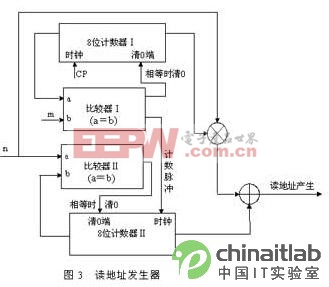

2.2.2 讀地址序列產(chǎn)生器設(shè)計(jì)

讀地址是整個(gè)交織器設(shè)計(jì)部分的關(guān)鍵,采用“亂序讀出”的方式。電路設(shè)計(jì)主要由加法、乘法器,計(jì)數(shù)器和比較器模塊構(gòu)成,其地址序列產(chǎn)生流程在算法分析中已作過詳細(xì)說明,這里只作簡單介紹:計(jì)數(shù)器Ⅰ相當(dāng)于變量j,首先在時(shí)間脈沖cp的驅(qū)動(dòng)下從初始狀態(tài)“00000000”開始遞增計(jì)數(shù),當(dāng)?shù)扔谠O(shè)定交織深度m時(shí),產(chǎn)生一個(gè)時(shí)鐘脈沖信號(hào)來驅(qū)動(dòng)計(jì)數(shù)器Ⅱ,此時(shí)計(jì)數(shù)器Ⅱ的計(jì)數(shù)加一,同時(shí)與另一設(shè)定數(shù)據(jù)n進(jìn)行比較,當(dāng)相等時(shí)計(jì)數(shù)器Ⅰ、Ⅱ同時(shí)清0,重新開始計(jì)數(shù)。

讀地址序列產(chǎn)生器

讀地址產(chǎn)生結(jié)果由數(shù)據(jù)n與計(jì)數(shù)器Ⅰ每次的輸出數(shù)據(jù)相乘,再與計(jì)數(shù)器Ⅱ的計(jì)數(shù)數(shù)據(jù)相加而得到。產(chǎn)生的序列依次為:0,n,2n,…,(m-1)n,1,n+1,2n+1,…,(m-1)n+1,2,…,mn-1.

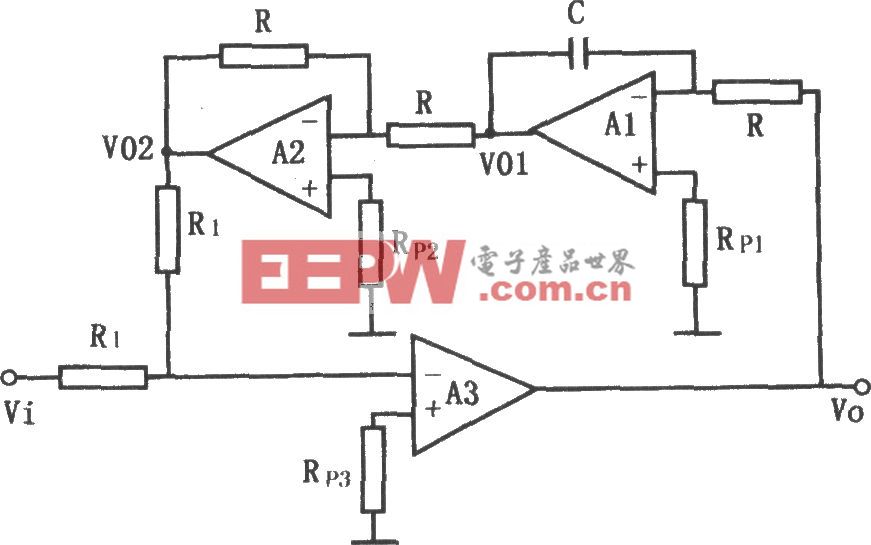

2.3 寫地址序列產(chǎn)生器設(shè)計(jì)

交織器采用“順序?qū)懭搿钡膶懙刂贩绞剑串a(chǎn)生“0,1,2 …,mn-1”的順序地址序列。因此寫地址序列產(chǎn)生器的實(shí)現(xiàn)可由乘法器,比較器和計(jì)數(shù)器等宏單元模塊構(gòu)成(如圖4所示),寫地址具體產(chǎn)生說明如下:

寫地址序列產(chǎn)生器

首先8位計(jì)數(shù)器在時(shí)鐘脈沖cp的驅(qū)動(dòng)下由初始狀態(tài)“00000000”開始遞增計(jì)數(shù),產(chǎn)生的計(jì)數(shù)數(shù)據(jù)分成兩路:一路送到雙端口RAM的寫地址端,作為交織器的寫地址產(chǎn)生信號(hào);另一路則送到比較器的一個(gè)輸入端,同乘法器輸出的結(jié)果進(jìn)行比較:當(dāng)計(jì)數(shù)器累計(jì)計(jì)數(shù)值小于乘法器計(jì)算結(jié)果時(shí),計(jì)數(shù)器繼續(xù)累加計(jì)數(shù);而當(dāng)計(jì)數(shù)值等于乘法器的計(jì)算結(jié)果時(shí),比較器產(chǎn)生中斷控制信號(hào)使得計(jì)數(shù)器清0,并重新開始計(jì)數(shù)。

評(píng)論