基于FPGA的改進(jìn)型分組交織器的設(shè)計與實(shí)現(xiàn)

2 改進(jìn)分組交織器的FPGA設(shè)計與實(shí)現(xiàn)

2.1 FPGA選取及總體實(shí)現(xiàn)

交織器的設(shè)計采用Altera公司生產(chǎn)的Cyclone系列FPGA實(shí)現(xiàn)。根據(jù)系統(tǒng)的總體要求選用了一片EP1C3T100C8芯片,該系列芯片具有成本低、設(shè)計靈活、系統(tǒng)便于集成等優(yōu)點(diǎn)[4],因而在數(shù)字通信系統(tǒng)設(shè)計中得到了廣泛的應(yīng)用。此外,Cyclone系列芯片內(nèi)部具有嵌入式RAM存儲空間,可以實(shí)現(xiàn)較為復(fù)雜的邏輯功能,當(dāng)用作片內(nèi)存儲器時,其存儲數(shù)據(jù)的寬度和深度可由設(shè)計人員設(shè)定。因而利用存儲器可以方便的設(shè)計出交織器,從而能夠大大減小電路的體積和復(fù)雜度。

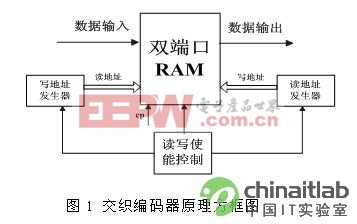

FPGA實(shí)現(xiàn)交織器的原理框圖如圖1所示,從圖中可以看出交織器主要由讀、寫地址序列發(fā)生器,雙端口RAM以及讀寫使能控制幾部分組成。其中讀寫使能控制主要用來產(chǎn)生雙端口RAM的讀寫控制信號,并決定讀、寫地址序列發(fā)生器何時啟動工作。

FPGA實(shí)現(xiàn)交織器的原理框圖

2.2 讀地址序列產(chǎn)生算法及設(shè)計

2.2.1 交織器讀地址產(chǎn)生算法

交織器設(shè)計的關(guān)鍵部分在于“讀/寫地址”的產(chǎn)生。設(shè)交織器的交織矩陣為n m矩陣,根據(jù)分組交織原理,輸入數(shù)據(jù)以0,1,2…,mn-1的順序地址方式寫入存儲器,交織后輸出為:0,n,2n,…, (m-1)n,1,n+1,2n+1, …,(m-1)n+1,2,…,mn-1.

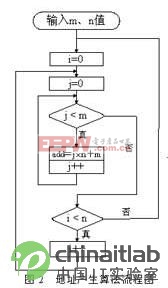

地址產(chǎn)生算法采用雙重循環(huán)的方式(算法流程如圖2所示),算法流程說明如下:

算法流程圖

①首先根據(jù)信道實(shí)際情況及數(shù)據(jù)幀長,選定合適的交織

將計數(shù)變量i,j清零;

②對計數(shù)變量j進(jìn)行判斷:如果j<m,則j++;

如果j=m,則跳到第3步;

③對計數(shù)變量i進(jìn)行判斷:如果i<n,則i++并將j清零之后跳回第2步;如果i=n,則跳回第1步,開始新一輪循環(huán)。

評論