利用EDA工具提高系統級芯片測試的效率

高度復雜的SoC設計正面臨著高可靠性、高質量、低成本以及更短的產品上市周期等日益嚴峻的挑戰。可測性設計通過提高電路的可測試性,從而保證芯片的高質量生產和制造。借助于EDA技術,可以實現可測試性設計的自動化,提高電路開發工作效率,并獲得高質量的測試向量,從而提高測試質量、低測試成本。

本文引用地址:http://www.104case.com/article/191825.htm

半導體工藝的進步以摩爾定率的速度推動著集成電路產業的發展。隨著芯片的工藝尺寸越來越細,集成度越來越高,半導體工藝加工中可能引入越來越多的各種失效。傳統的利用功能仿真向量進行生產制造芯片的后期測試,雖然有的工程師認為由于充分測試過電路的功能,所以功能測試向量應該可以滿足市場對產品質量的需求,然而實際上功能測試向量還很不完備,亞微米、深亞微米制造工藝條件下,功能測試向量所能達到的測試覆蓋率只有50%到60%左右,測試的質量得不到充分保證;另外功能測試向量的產生和運行都十分昂貴;與此同時功能測試向量還不便于失效器件的故障診斷。

可測試性設計的內容與EDA技術

半導體工藝中可能引入各種失效,材料的缺陷以及工藝偏差都可能導致芯片中電路連接的短路、斷路以及器件結間穿通等問題。而這樣的物理失效必然導致電路功能或者性能方面的故障,對這些電學故障進行邏輯行為抽象就稱為故障模型。例如,最常用的一種類型的電學故障可以抽象為單元中的信號狀態被鎖定在邏輯“0”或者邏輯“1”上(SA0或者SA1),這種類型物理失效的抽象模式被稱為“Stuck-at”的故障模型;對于深亞微米制造工藝的芯片,其高性能的測試中還必須結合多種實速(at-speed)故障模型,包括躍遷故障模型、路徑延時故障模型和IDDQ故障模型等。

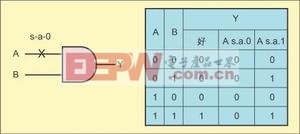

Stuck-at故障模型示例如圖1所示,其測試向量及測試結果的判斷如該真值表所示。通常情況下,多數工藝失效問題都可以通過利用stuck-at故障模型測試到。

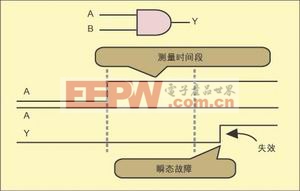

躍遷故障模型包括慢上升(Slow-to-Rise)和慢下降(Slow-to-Fall)兩種類型。我們以慢上升故障模型為例來說明躍遷故障模型的測試。如圖2所示,觀測窗口是電路正常工作所允許的最大躍遷延遲時間,測試時如果在觀測窗口時間段內撲獲不到期望的輸出,則認為被測試節點存在躍遷故障。

路徑延時故障模型與躍遷故障模型類似,不同的是利用路徑延時故障模型測試的電路的某一路徑的集中延時情況。 如圖3所示,路徑延時故障模型測試的對象是一條時序路徑,通過對路徑的輸入端賦值進行觸發,然后在特定的觀測時間窗口內、在路徑輸出端捕獲期望輸出。

如圖3所示,路徑延時故障模型測試的對象是一條時序路徑,通過對路徑的輸入端賦值進行觸發,然后在特定的觀測時間窗口內、在路徑輸出端捕獲期望輸出。

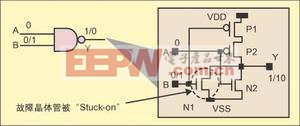

IDDQ故障模型利用在電路穩態情況下觀測電源的靜態漏電流的變化情況達到測試電路失效故障的目的。如圖4所示,如果電路的B節點存在SA1故障,晶體管N1處于常開啟狀態,測試時會發現改變B節點的輸入激勵,電源的靜態漏電流的變化不大。

可測性設計(DFT)就是確保設計的電路具備更高的可測試性并且自動產生高質量的測試向量集;其目的就是為了確保ASIC/SOC芯片在生產制造之后,通過測試的產品都能夠正確無誤地工作。可測性設計的內容主要包括:1. 測試綜合:芯片設計過程中DFT在設計中自動插入測試結構,確保生產加工后的芯片易于測試。2. ATPG:利用EDA工具自動產生可以在ATE上運行的測試向量,利用EDA工具自動診斷導致元器件失效的故障產生的原因。3. BIST:利用EDA工具自動生成被測電路的測試用IP,完成測試序列生成和輸出響應分析兩個任務,通過分析被測電路的響應輸出,判斷被測電路是否有故障。

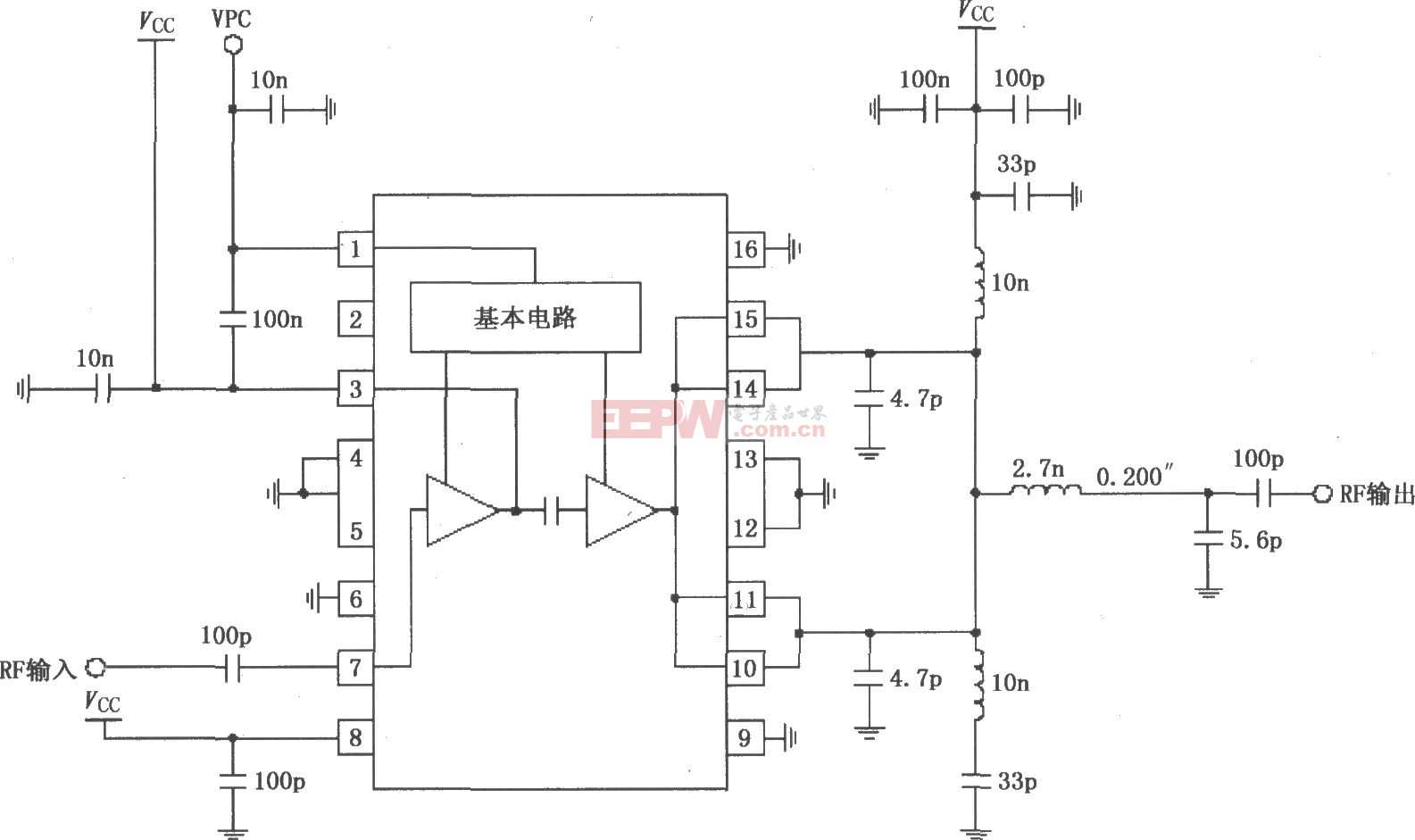

如圖5所示是DFT解決方案:對全掃描邏輯電路的測試,設計者可以選用Fastscan,對部分掃描邏輯電路的測試,設計者可以選用Flextest,對IP或宏模塊的內建自測試,設計者也可以選用LBISTArchitect。對Memory的測試,設計者可以選用MBISTArchitect,也可以選用fastscan的子模塊功能Macrotest。采用邊界掃描電路的設計,設計者可以選用BSDArchitect。

測試綜合完成自動插入全掃描或部分掃描的測試邏輯,大大增強了IC和ASIC設計的可測試性。它在設計過程的早期階段進行可測性分析,在測試向量生成和掃描自動綜合之前發現并修改違反測試設計規則的問題,盡可能提高ATPG的效率并縮短測試開發的周期。

測試綜合工具DFTAdvisor利用友好的圖形用戶界面引導完成可測性分析,執行全面的測試規則檢查,完成并優化掃描邏輯插入,保證在ATPG之前不存在任何遺留的可測性問題。其主要特點如下:

1. 支持智能化的、層次化的測試邏輯的自動化插入;

2. 通過密集的基于仿真的測試規則檢查(超過140條測試規則)來確保高效率的可測性分析;在設計的早期階段,發現并糾正設計中影響可測性的問題;

3. 支持Mux-DFF、Clocked-Scan和LSSD掃描結構;

4. 同時支持全掃描與部分掃描的識別與插入;提供了多種可選的部分掃描插入方式,并可自動選擇部分掃描方式;

5. 通過自動測試點插入與綜合來加強設計的可測性;

6. 通過插入測試邏輯電路來自動糾正設計中違反可測性設計規則的部分;

7. 支持版圖層次上的掃描鏈單元的次序控制,以提高測試邏輯插入過程中的時序有效性;

8. 為后續的ATPG過程提供充分支持,生成ATPG工具要求的全部SETUP文件,可直接調用ATPG 工具確保快速DFT流程;

9. 支持UNIX平臺(Solaris, HP-PA) 及LUNIX操作平臺。

評論