在40-nm 工藝節點實現世界上最先進的定制邏輯器件

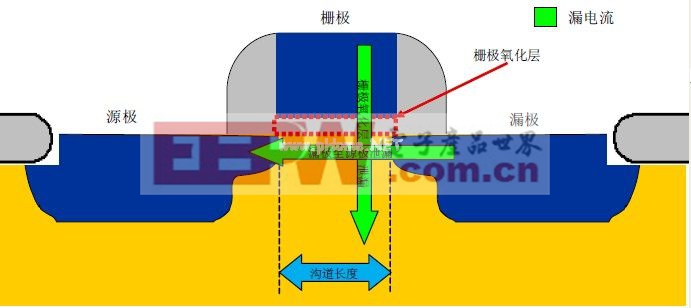

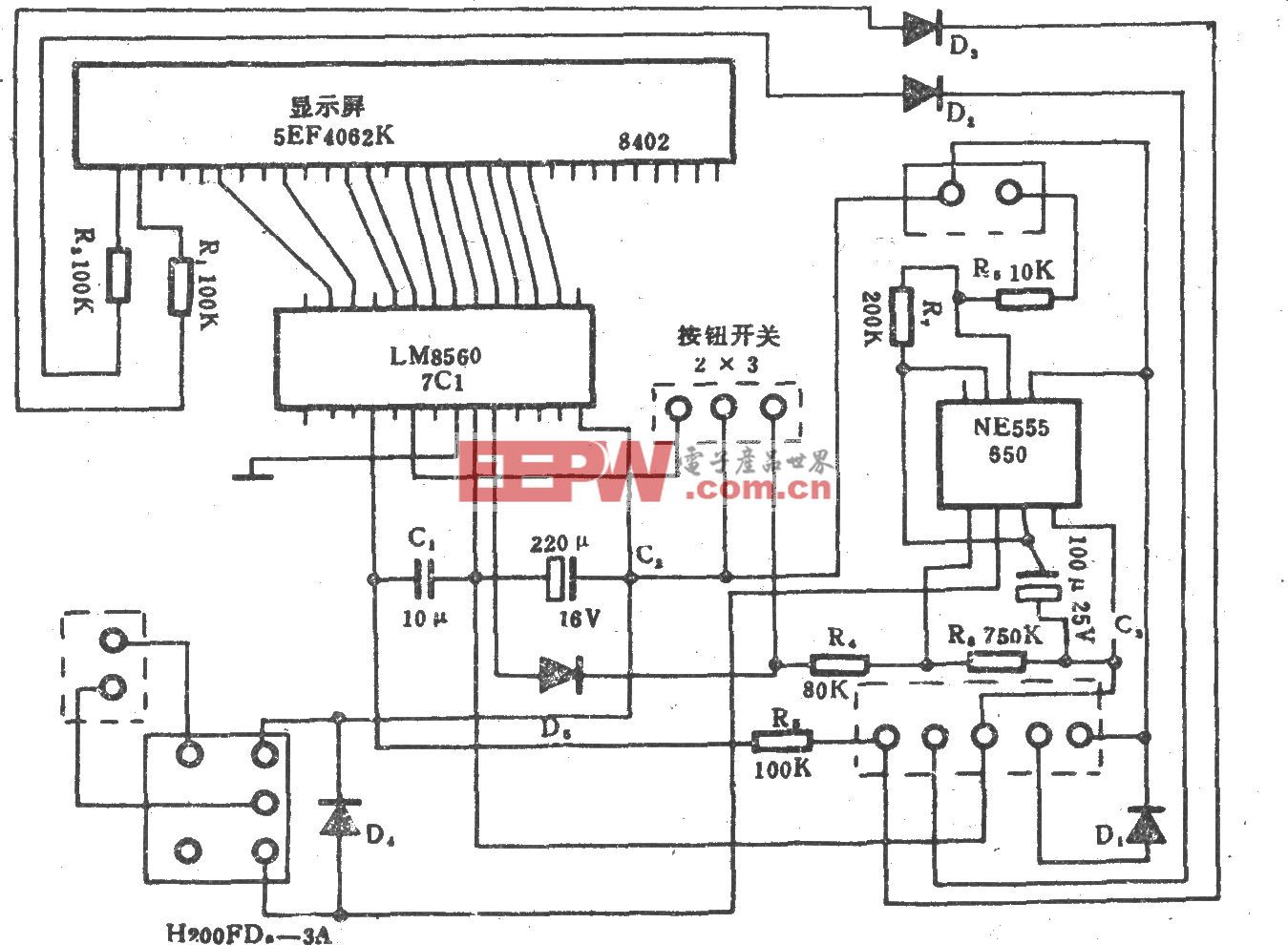

在深亞微米,隨著向高級工藝的過渡,由于靜態功耗顯著增大,半導體功耗成為非常關鍵的問題。物理距離減小更容易出現電流泄漏。漏極至源極泄漏和柵極泄漏都與溝道長度和邏輯門氧化層厚度成反比,隨著長度和厚度的減小會顯著增大( 圖2)。

NMOS

PMOS

Altera 公司 在40-nm 工藝節點實現世界上最先進的定制邏輯器件

3本文引用地址:http://www.104case.com/article/191799.htm

圖2. 晶體管源極漏電流

源極至漏極泄漏也被稱為亞閾值泄漏,是漏電流的主要因素。在這里,即使晶體管邏輯門關斷,電流也會從晶體管源極流向漏極。由于晶體管越來越小,很難防止出現這類電流,因此,在其他參數都相同的條件下,較小的40-nm 晶體管比大工藝尺寸的晶體管更容易出現源極至漏極泄漏,而且漏電流更大。

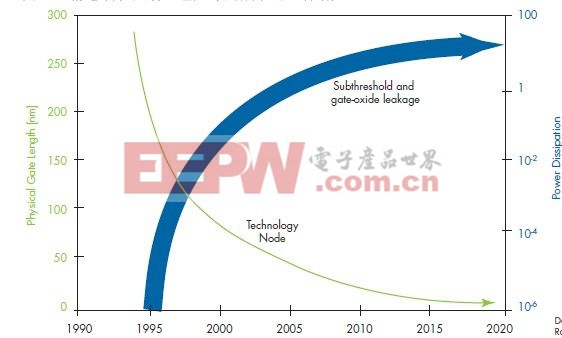

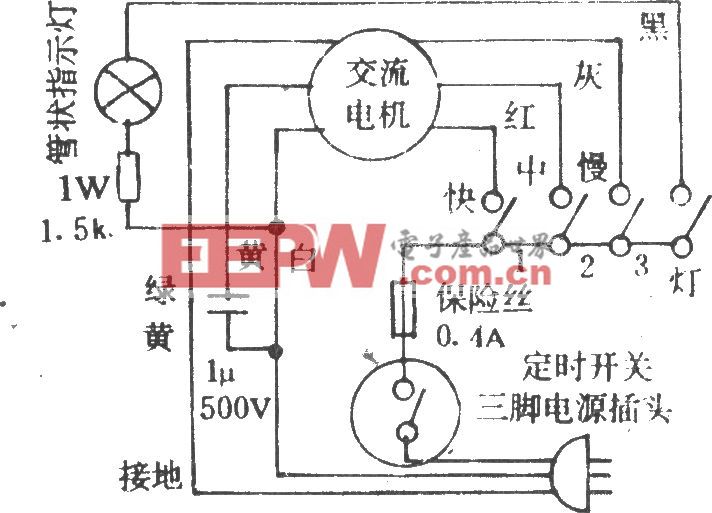

晶體管閾值電壓(Vt) 也會影響源極至漏極泄漏的大小。晶體管Vt 是溝道開始傳導柵極和源極之間電流的電壓值。較小的高速晶體管需要較低的Vt 通過柵極控制來保持晶體管打開和關斷的速率,但是由于晶體管溝道不能徹底關斷,這也會增加漏電流。另一問題是柵極氧化層的厚度,它和攙雜一起也會影響Vt。較薄的氧化層使晶體管能夠更迅速地開關,但是也增加了從柵極到基底氧化層的漏電流。隨著工藝尺寸的減小,邏輯門長度越來越短,這些漏電流在增大,如圖3 所示。

圖3. 靜態功耗隨著工藝尺寸的減小而顯著增大

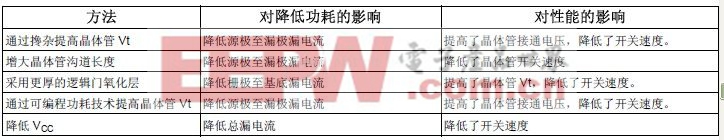

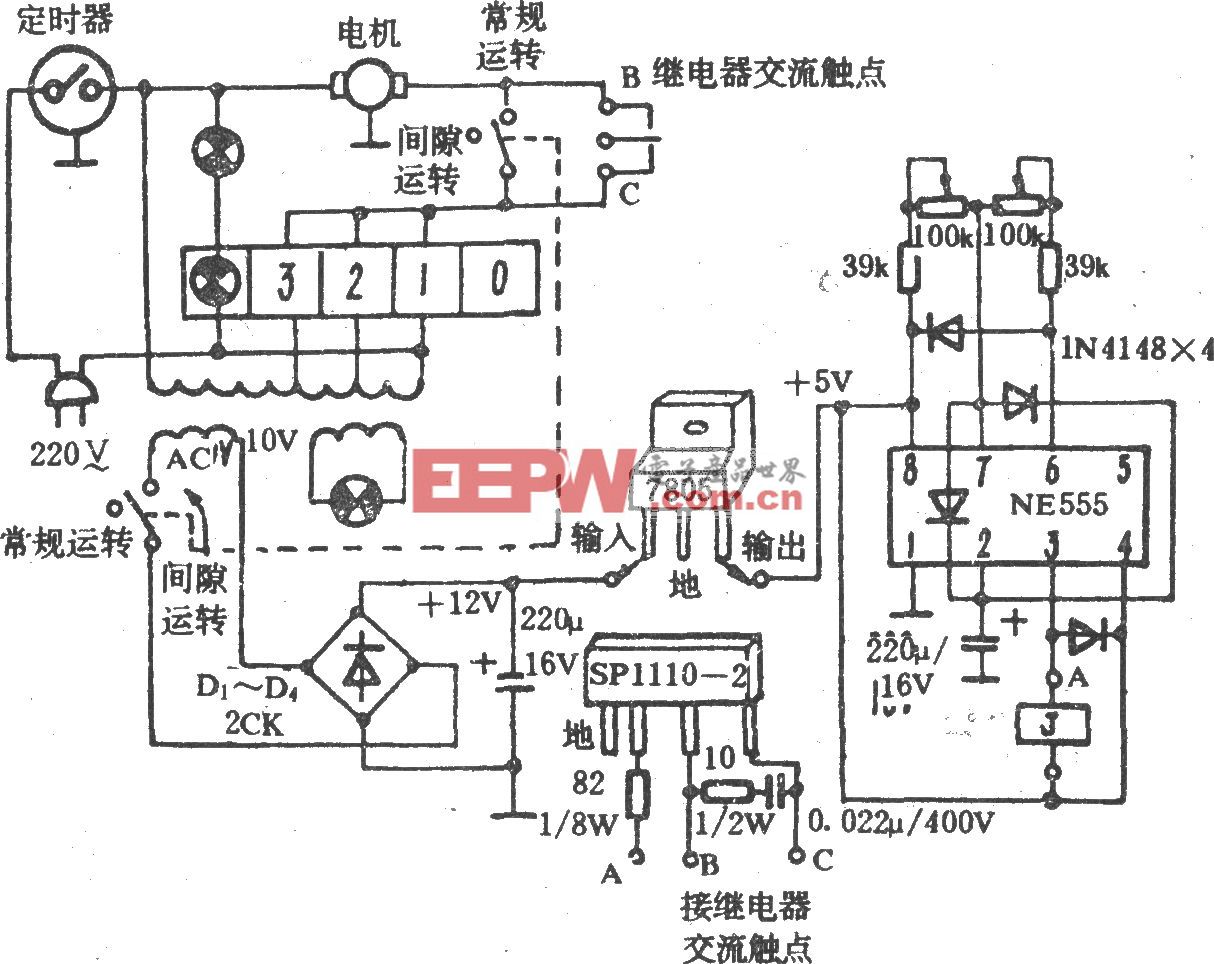

Altera 主要采用5 種方法來降低漏電流,如表3 所示。

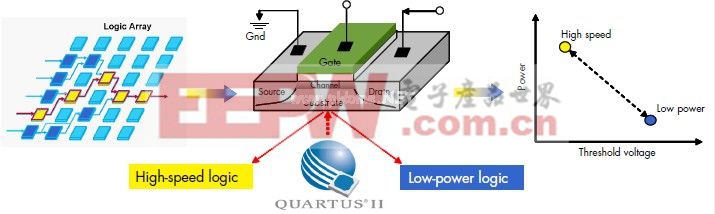

所有方法都對性能有影響,使晶體管不能以最大速率工作。然而, Altera 進行了明智的選擇,在晶體管級以性能換取低功耗,維持器件總體性能不變。通過分析除了上面介紹的5 種方法, Altera 采用了其獨特的可編程功耗技術來降低靜態功耗。這一專利功能內置在Stratix IV 器件芯片中,使Quartus® II 開發軟件能夠根據設計要求,改變晶體管Vt,以平衡性能和功耗。圖4所示為可編程功耗技術的高級實現, Quartus II 軟件根據時序驅動的編輯功能分析用戶FPGA 設計,選擇邏輯陣列中的哪些晶體管應該采用高速模式,哪些應該采用低功耗模式。通過改變跨過反向偏置電壓的晶體

管Vt,減小了時序不重要通路上的晶體管泄漏( 增大Vt),從而實現了低功耗,同時在需要的地方保持高性能不變。

圖4. 可編程功耗技術 (1) 通過設置晶體管反向偏置,平衡了功耗/ 性能。

注釋:

(1) 這是可編程功耗技術非常簡單的“模型”。實際情況各種各樣,并擁有專利。

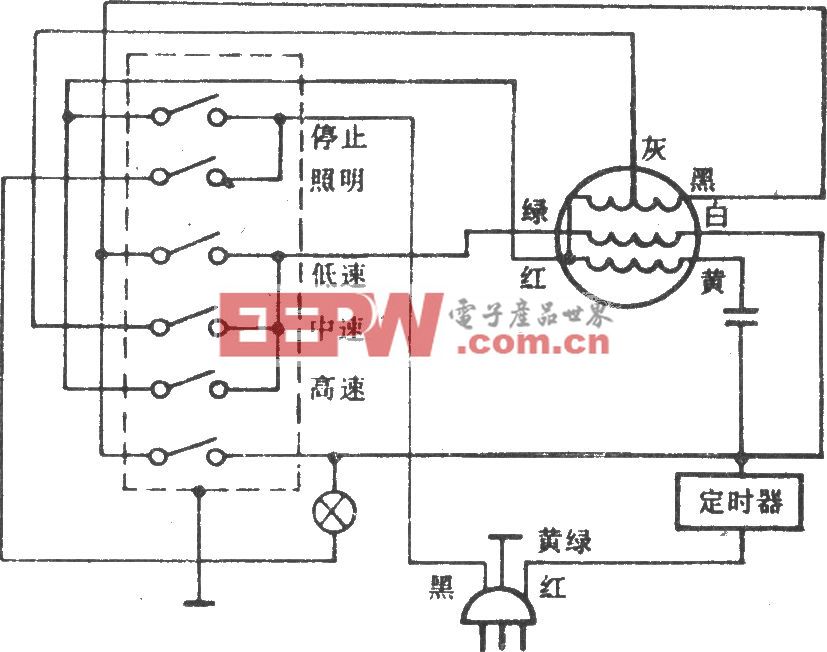

為降低器件的動態功耗,在40-nm 器件上, Altera 將以前器件系列使用的1.1V 內核電壓降到了0.9V。晶體

管開關期間消耗的功率與V2C ( 其中, C 是電容) 成正比,因此,降低供電電壓會導致動態功耗按平方比

例下降。

減小內核電壓也會影響晶體管性能,但是Altera 再次利用了40-nm 節點的高性能特性來保持器件級性能不變。如前所述,和以前的工藝節點相比, Altera 在40-nm 節點某些晶體管上具有更強的驅動能力, IC 設計人員能夠在驅動能力和降低功耗上達到平衡。

此外, Altera 在其收發器上降低了每個發送器和接收器通道的功耗,進一步降低了總功耗。Altera Stratix

IV FPGA還通過動態片內匹配(OCT) 技術降低了有功功耗。采用動態OCT后,可以根據需要來接通或者關斷Altera 器件中的匹配電阻。在存儲器讀/ 寫周期中,關斷不需要的匹配電阻,去掉了電阻上的壓降,對于72 位接口,功耗能夠降低1.2 瓦。

表3. Altera 降低漏電流采取的方法

方法對降低功耗的影響對性能的影響

通過攙雜提高晶體管Vt 降低源極至漏極漏電流提高了晶體管接通電壓,降低了開關速度。

增大晶體管溝道長度降低源極至漏極漏電流降低了晶體管開關速度

采用更厚的邏輯門氧化層降低柵極至基底漏電流提高了晶體管Vt,降低了開關速度。

通過可編程功耗技術提高晶體管Vt 降低源極至漏極漏電流提高了晶體管接通電壓,降低了開關速度。

降低VCC 降低總漏電流降低了開關速度

5

總之, Altera 在Arria II GX 器件上采取低功耗技術后,實現了帶有3.75-Gbps 收發器、功耗最低的FPGA,其功耗比競爭器件低65%。對于Stratix IV FPGA,采取低功耗措施后,和65-nm Stratix III FPGA 中實現的相似設計相比,總功耗( 待機功耗 + 動態功耗) 平均降低了30%。

從技術領先到平穩提高產量成功推出首款40-nm FPGA 是非常重要的事件,但是Altera 的目標不止于此,還要象以前工藝節點產品那樣,實現高質量可靠交付。通過努力, Altera 依靠其可靠的開發實踐,包括強大的測試芯片計劃、嚴格的器件檢驗程序以及在提高產量上的獨特優勢,獲得了極大的成功。所有這些方面都得到了業界堅實的代工線合作伙伴的有力支持。

Altera 的代工線合作伙伴TSMC 是代工線市場的領先者。在專業代工線領域,TSMC 占據了50%以上的世界市場份額,年度研究和開發投入超出最相近競爭對手55%。這些投入使TSMC 在光刻和可生產性設計(DFM) 方面占據了業界領先位置,進一步保證了TSMC 能夠成功交付高級工藝節點產品。最重要的是,在40-nm 節點, TSMC 是浸入式光刻技術的領先者,該工藝結合光刻透鏡和清澈液體,透過分辨率更高的光線,實現了更小、封裝更緊湊的器件。浸入式光刻是大部分半導體公司開發45-nm 節點及后續節點技術所選用的工藝,普遍認為也是32-nm 節點要采用的技術。

和TSMC 一起, Altera 積極組織了多個聯合工藝開發團隊,以解決工藝開發面臨的各種問題,包括功耗/性能、建模、測試芯片規劃、存儲器、可靠性、聚乙烯熔絲、DFM、RF/ 模擬、ESD 和封裝等。所有團隊在雙方產品交付和先進性上達成一致,精誠合作,堅持到底。

業界最可靠的測試芯片技術Altera 的實踐表明,在130nm、90nm 和65-nm 器件生產中,對于新半導體工藝體系結構和器件特性的早期評估以及精細加工,測試芯片技術是非常有價值的工具。這一策略使Altera 的器件產量穩步上升,已經證明是可編程邏輯行業最具特色的一點。在40-nm 節點, Altera 以可靠的9 種測試芯片計劃為其最新一代產品獲得成功再次建立了強大的基礎。

由于需要大量的模板,采用測試芯片意味著較大的投入。Altera 與TSMC 密切合作,保持了工藝效率,降低了成本。例如, TSMC 自己制造大量的測試晶片,全面進行特性測試,調整制作方法,然后監控產品。

通過密切合作,在代工線晶片早期階段實現了“背負式”測試結構,縮短了Altera 產品投產時間,使客戶能夠盡早使用最先進的技術。同樣的,在Altera 的幫助下, TSMC 能夠有機會使用其模板進行更多的測試。結果對雙方都有好處。

通過采集并分析測試芯片數據, Altera 深入研究了各種隨機和系統偏差的影響,開發設計策略來降低甚至消除這些不利影響。Altera 在測試芯片上的大量投入幫助客戶避免了前沿半導體設計中的風險。對風險管理的關注展示了Altera 在可靠交付新技術產品上的承諾, Altera 不會中斷或者以有限的產量向客戶供貨,也不會提供達不到要求的產品。

評論