在40-nm 工藝節(jié)點實現(xiàn)世界上最先進的定制邏輯器件

引言

Altera于2008年第二季度推出Stratix® IV和HardCopy® IV器件系列標志著世界上首款40-nm FPGA和業(yè)界唯一40-nm ASIC 無風險移植途徑的誕生。Altera 通過三年周密的規(guī)劃和開發(fā),并與代工線合作伙伴臺積電(TSMC) 協(xié)作,最終獲得成功,交付定制邏輯器件展示了無可爭議的產(chǎn)品領先優(yōu)勢。Altera 隨后于2009 年第一季度發(fā)布Arria® II GX 和Stratix IV GT FPGA 系列,實現(xiàn)了業(yè)界最全面的收發(fā)器系列產(chǎn)品。表1 所示為Altera 開發(fā)世界上首款40-nm FPGA 的歷史過程。

40-nm 工藝節(jié)點非常重要,它為Altera 在性能最好、密度最大、功耗最低、性價比最高FPGA 和HardCopyASIC 上保持領先優(yōu)勢打下了堅實的基礎。

40-nm 工藝技術的重要性

40-nm 工藝要比以前包括65-nm 節(jié)點和最近的45-nm 節(jié)點在內(nèi)的工藝技術有明顯優(yōu)勢。最引人注目的優(yōu)勢之一是其更高的集成度,半導體生產(chǎn)商可以在更小的物理空間中實現(xiàn)更強的功能。國際電子器件大會(IEDM) 報告了密度提高所得到的實際結果,主要的半導體生產(chǎn)商展示了他們在工藝技術上努力的結果。

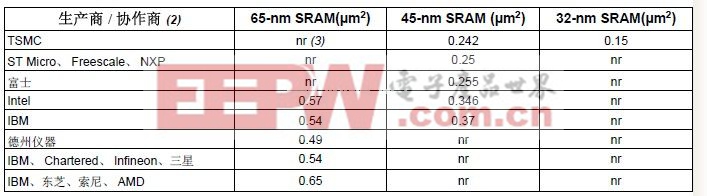

對SRAM 單元大小進行了基準測試,表2 列出了上次IEDM 大會報道的最近工藝節(jié)點的SRAM 單元大小(以45-nm 工藝單元大小遞增的順序列出)。如表中所示,工藝技術的提高使半導體生產(chǎn)商能夠在更小的面積上實現(xiàn)更強的功能。

注釋:

(1) 來源:Real World Technologies, “Process Technology Advancements at IEDM 2007”

(2) 僅列出了報道65-nm 或者45-nm SRAM 單元大小的公司/ 組織

(3) nr = 沒有報道

表1. Altera 40-nm 器件的開發(fā)過程

日期里程碑

2005 年第一季度Altera 啟動40-nm FPGA 和HardCopy ASIC 系列開發(fā),在40-nm 工藝上開始與TSMC 合作。

2005 年第四季度Altera 的第一組9 種40-nm 器件測試芯片投片

2006 年第二季度測試芯片結構評估

2007 年第四季度TSMC 發(fā)布產(chǎn)品級45-nm 工藝,加強與Altera 的合作。

2008 年第一季度TSMC 發(fā)布40-nm 工藝

2008 年第二季度Altera 發(fā)布世界上首款40-nm FPGA, Stratix IV 器件系列和首款40-nm HardCopy IV ASIC。

2009 年第一季度Altera 發(fā)布最全面的收發(fā)器系列產(chǎn)品,包括Arria II GX 和Stratix IV GT FPGA。

表2. 65-nm 和45-nm 工藝節(jié)點報道的最小SRAM 單元 (1)

在40-nm 工藝節(jié)點實現(xiàn)世界上最先進的定制邏輯器件Altera 公司

2

40-nm 工藝還具有明顯的性能優(yōu)勢。40 nm晶體管邏輯門長度比65 nm 邏輯門長度短38.5%,比45-nm 工藝邏

輯門長度短11%。相應的低阻抗提高了40 nm 的驅(qū)動能力,意味著性能更好的晶體管。

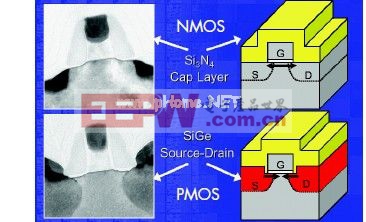

Altera 使用應變硅技術進一步提高了性能。例如, Altera 器件利用了NMOS 晶體管保護層的拉伸應變以及

PMOS 晶體管源極和漏極攙雜硅鍺的壓縮應變( 參見圖1)。這些應變硅技術將電子和空穴的移動能力提高了

30%,使晶體管性能提高了近40%。

圖1. 40 nm 應變硅技術實現(xiàn)了性能更好的晶體管

密度和性能的提高意義非常大,而當今系統(tǒng)開發(fā)人員面臨的最大設計問題之一是功耗。40-nm 節(jié)點在這方面也有一定的優(yōu)勢,更小的工藝尺寸減小了產(chǎn)生動態(tài)功耗的雜散電容。特別是, TSMC 的40-nm 工藝技術比45-nm 工藝技術有功功率降低了15%。

然而,如果不采取措施,工藝尺寸的減小會增大待機功耗。為解決這些問題以及其他越來越多的功耗問題,Altera 采取了積極的措施來降低40-nm 器件的有功功耗和待機功耗。

結合領先的工藝和器件體系結構滿足關鍵的系統(tǒng)設計需求過渡到40-nm 節(jié)點實現(xiàn)了摩爾定律預言的密度和性能優(yōu)勢。利用這些工藝優(yōu)勢并結合器件體系結構創(chuàng)新,Altera 繼續(xù)為業(yè)界提供密度最大、性能最好的定制邏輯器件。由此, Altera® Stratix IV FPGA 和HardCopy IVASIC 分別能夠提供650K邏輯單元(LE) 和13M ASIC 邏輯門。在性能方面,Altera 40-nm器件系列邏輯性能達到了600-MHz,收發(fā)器性能高達8.5 Gbps,同時, 1.6 Gbps 的LVDS I/O 和1066 Mbps 的單端I/O 性能都是業(yè)界最好的,所有這些都不以犧牲信號完整性為代價。

除了最高的密度和最好的性能, Altera 還致力于實現(xiàn)最低的功耗。當今小外形緊湊封裝、便攜性以及功效的發(fā)展趨勢推動了對低功耗的需求。產(chǎn)品系統(tǒng)外形非常薄,體積非常小,限制了空氣對流、熱沉以及其他的散熱管理解決方案。此外,很多應用首先考慮的問題是功率元件的工作成本,這促使低功耗成為最明顯的競爭優(yōu)勢,是很多應用中必須要考慮的問題。設計目標在這方面的變化使得功耗成為選擇系統(tǒng)元件時首先要考慮的標準。

FPGA 供應商的器件在功能越來越強的電路板上發(fā)揮的作用也越來越大,在很多情況下要實現(xiàn)系統(tǒng)核心功能,器件功耗管理的難度也隨之增大。需要很大的投入才能在提高性能和降低功耗上達到平衡。

評論