基于FPGA的自適應鎖相環設計

鎖相環啟動工作時,不論噪聲水平高低,鑒相器輸出信號的抖動都比較大,連續3次抖動高于上限值是比較正常的,這時若將帶寬值減小,會降低跟蹤速度。因此設計中限定,只有本振信號的相位和接收載波信號的相位大致相符后,才允許減小帶寬值。因此環路設計中需要判斷相位是否大致相符。

參看結構圖l,經低通濾波后的同相和正交支路的信號分別為:。相位大致相符時,取值較小,I(t)2應大于Q(t)2。設計中利用條件判斷是否已滿足相位大致相符的條件。二者之差的下限值c同樣與系統中的輸入數據位數、濾波器等模塊有關系,可在Modelsim或Quartus下通過測試獲得。為了增加判斷的準確性,設計中同樣做出限定,連續3次滿足條件時,才判定相位已大致相符。

5 實驗結果及分析

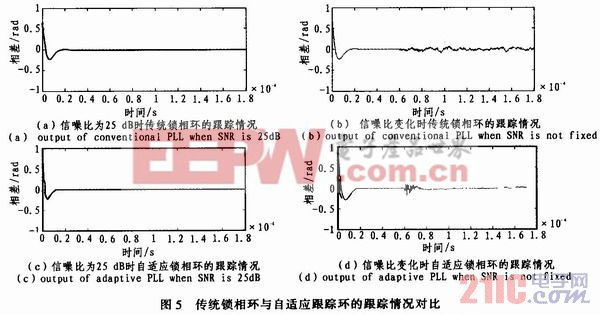

設置中頻載波信號為10 MHz,采樣頻率為80 MHz,本地初始中心頻率為9.9 MHz。在信噪比固定為25 dB和信噪比變化的情況下,分別利用傳統的鎖相環和圖2所示的自適應鎖相環進行相位跟蹤,得到的相差結果如圖5所示。

通過仿真結果(圖5)可以看出,與傳統鎖相環相比,自適應鎖相環能夠根據當前環境自適應對環路帶寬作出調整,對環境的適應性更強。噪聲水平較低時,跟蹤速度是關鍵性能參數。在噪聲水平較低的情況下(對應25 dB),自適應跟蹤具有更快的跟蹤速度。噪聲水平較高時,相位抖動是關鍵參數,結果顯示,在噪聲水平較高的情況下,自適應鎖相環具有較小的抖動。

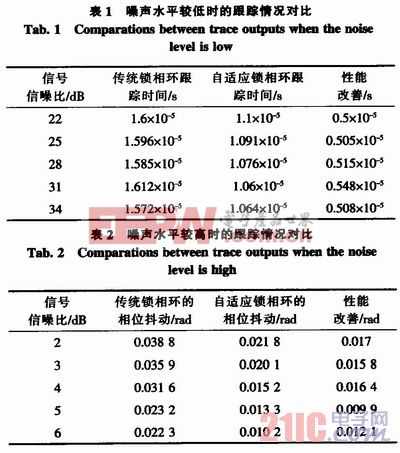

在此基礎上,在多種信噪比環境下進行實驗。信噪比較大即噪聲水平較低時,傳統鎖相環的自適應跟蹤的跟蹤速度結果如表1所示。信噪比較小即噪聲水平較高時,傳統鎖相環的自適應跟蹤的跟蹤速度結果如表2所示。

上述結果顯示,與傳統鎖相環相比,自適應鎖相環在噪聲水平較高時,具有更快的跟蹤速度,在噪聲水平較低時,最有更小的相位抖動,起到了根據環境作出自適應調整的作用。

系統設計中使用的FPGA是EP3CIOF256C8。將調試好的程序下載到FPGA硬件板,通過QUARTUSⅡ軟件中自帶的SIGNALTAP工具對輸入和輸出信號進行實時觀察,結果顯示,設計的自適應鎖相環能夠進行正確穩定的跟蹤,正確解調出數據信號。該模塊目前已應用在基于數字中頻方案的擴頻接收機中。

6 結論

在傳統鎖相環的基礎上,引入自適應參數調整模塊,能夠根據鎖相環所處環境的噪聲情況,自適應地對環路帶寬進行調整,由于調整過程中步長取值較小,具有一定的連續性,因此,調整過程中仍能正常進行數據解調,不會引起突變,能夠有效地在噪聲性能和跟蹤速度間進行平衡。

本文引用地址:http://www.104case.com/article/191454.htm

評論