基于FPGA的人工神經(jīng)網(wǎng)絡(luò)系統(tǒng)的實(shí)現(xiàn)方法

摘要:為了改變人工神經(jīng)網(wǎng)絡(luò)的研究?jī)H僅局限于算法,只是在通用的串行或并行計(jì)算機(jī)上模擬實(shí)現(xiàn)的現(xiàn)狀,針對(duì)函數(shù)逼近問(wèn)題,將BP神經(jīng)網(wǎng)絡(luò)的結(jié)構(gòu)分為3個(gè)模塊,采用VHDL語(yǔ)言完成對(duì)各個(gè)模塊的硬件描述,并使用Altera公司的QualtusII 6.1綜合軟件進(jìn)仿真和調(diào)試,然后在Cyc-loneII系列FPGA上實(shí)現(xiàn)了能夠進(jìn)行片上學(xué)習(xí)并完成函數(shù)逼近的BP神經(jīng)網(wǎng)絡(luò)系統(tǒng)。測(cè)試結(jié)果證明,該系統(tǒng)能夠很好地完成在線學(xué)習(xí),并能滿足一般系統(tǒng)應(yīng)用的速度和精度的要求,驗(yàn)證了該方法的有效性。

關(guān)鍵詞:神經(jīng)網(wǎng)絡(luò);硬件實(shí)現(xiàn);FPGA;片上學(xué)習(xí);函數(shù)逼近

神經(jīng)網(wǎng)絡(luò)是由大量的神經(jīng)元通過(guò)特殊形式的加權(quán)網(wǎng)絡(luò)相互聯(lián)接而形成的,可以認(rèn)為:神經(jīng)網(wǎng)絡(luò)由兩種基本單元構(gòu)成,即收集信號(hào)并且完成非線性變換的神經(jīng)元胞,以 及完成各神經(jīng)元之間的加權(quán)互連的突觸。標(biāo)準(zhǔn)的神經(jīng)網(wǎng)絡(luò)VLSI的實(shí)現(xiàn)方式是在單個(gè)芯片上集成多個(gè)神經(jīng)元和突觸單元,并且將它們按某種通信結(jié)構(gòu)組成神經(jīng)網(wǎng)絡(luò) 系統(tǒng),此外,還有基于ASIC結(jié)構(gòu)的,針對(duì)神經(jīng)網(wǎng)絡(luò)運(yùn)算特點(diǎn)進(jìn)行優(yōu)化和簡(jiǎn)化設(shè)計(jì)的FPGA

實(shí)現(xiàn)方式,以及基于商業(yè)處理器(如數(shù)字信號(hào)處理、RISC單片處理等)的模擬神經(jīng)網(wǎng)絡(luò)的多處理器結(jié)構(gòu)的實(shí)現(xiàn)方式。

衡量一個(gè)神經(jīng)網(wǎng)絡(luò)性能的重要指標(biāo)是快速性和適用性,而FPGA的集成度已經(jīng)達(dá)到百萬(wàn)門級(jí),用FPGA構(gòu)造神經(jīng)網(wǎng)絡(luò)時(shí),可以靈活地實(shí)現(xiàn)各種運(yùn)算功能和學(xué)習(xí)規(guī) 則,并且設(shè)計(jì)周期短、系統(tǒng)速度快、可靠性高、輸入輸出接口靈活、幾乎可以和任何形式的并行、串行接口及并行、串行A/D或D/A,DSP等連接,同時(shí)由于 可以將整個(gè)系統(tǒng)都集成在單個(gè)芯片內(nèi),因而抗干擾性能極強(qiáng),使其在自動(dòng)控制、故障診斷、模式識(shí)別,圖像獲取、DSP應(yīng)用、嵌人式系統(tǒng)等領(lǐng)域有著廣泛的應(yīng)用前 景。所以,F(xiàn)PGA無(wú)疑是首選的實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)的硬件芯片。

1 BP神經(jīng)網(wǎng)絡(luò)的基本原理

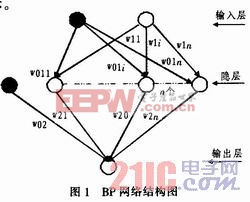

BP人工神經(jīng)網(wǎng)絡(luò)即誤差后向傳播網(wǎng)絡(luò),是一種前饋網(wǎng)絡(luò),由輸入層、隱含層和輸出層構(gòu)成。隱含層通過(guò)作用函數(shù)執(zhí)行一種固定不變的非線性變化,將輸出空間映像 到一個(gè)新的空間,輸出層節(jié)點(diǎn)則在該新空間進(jìn)行線性加權(quán)組合。BP算法用于多層網(wǎng)絡(luò),對(duì)于線性情況,多層網(wǎng)絡(luò)可以簡(jiǎn)單到只有一個(gè)輸入層節(jié)點(diǎn)和輸出層節(jié)點(diǎn),而 沒(méi)有隱含層(中間層)。實(shí)際上,大多數(shù)自然、經(jīng)濟(jì)和社會(huì)系統(tǒng)及其影響因素是非常復(fù)雜的非線性系統(tǒng),它不僅有輸入層節(jié)點(diǎn)及輸出層節(jié)點(diǎn),而且還可以有一層至多 層隱含層節(jié)點(diǎn)。權(quán)值為零,說(shuō)明相連的兩個(gè)神經(jīng)元不發(fā)生作用,若為負(fù),說(shuō)明相連的兩個(gè)神經(jīng)元之間相互抑制。此外,對(duì)于隱含層及輸出層的各神經(jīng)元而言,它還有 一個(gè)閾值,其作用是調(diào)節(jié)神經(jīng)元的興奮水平。當(dāng)有信息輸入網(wǎng)絡(luò)時(shí),該信息首先由輸入層傳至隱含層節(jié)點(diǎn),經(jīng)特性函數(shù)作用后,再傳至輸出層輸出,其間每經(jīng)過(guò)一層 都要由相應(yīng)的特性函數(shù)進(jìn)行變換。節(jié)點(diǎn)的特性函數(shù)要求是可微的,通常選用S型函數(shù),特性函數(shù)通常取Sigmoid函數(shù),本系統(tǒng)選用Sigmoid函數(shù),即![]() 和

和![]() 作為特性函數(shù),具有較好的收斂性,模擬結(jié)論也比較符合實(shí)際情況。

作為特性函數(shù),具有較好的收斂性,模擬結(jié)論也比較符合實(shí)際情況。

2 BP學(xué)習(xí)算法描述

BP網(wǎng)絡(luò)中每個(gè)節(jié)點(diǎn)都有一個(gè)狀態(tài)變量xi,節(jié)點(diǎn)i到節(jié)點(diǎn)j有一個(gè)連接權(quán)系數(shù)wji,每個(gè)節(jié)點(diǎn)都有一個(gè)閾值θj,每一個(gè)節(jié)點(diǎn)定義一個(gè)變換函數(shù)fj[xi,wji,θj(i≠j)],最常見的形式為

為了方便起見,將閾值θ作為神經(jīng)元權(quán)值的第一個(gè)分量加到權(quán)值中去,那么輸入向量就應(yīng)增加一項(xiàng),可設(shè)輸入向量的第1個(gè)分量固定為l,這樣 的形式就可變?yōu)?img onload="if(this.width>620)this.width=620;" onclick="window.open(this.src)" style="cursor:pointer" border="0" src="http://editerupload.eepw.com.cn/fetch/20131118/191453_1_4.jpg" alt="e.JPG" />。

的形式就可變?yōu)?img onload="if(this.width>620)this.width=620;" onclick="window.open(this.src)" style="cursor:pointer" border="0" src="http://editerupload.eepw.com.cn/fetch/20131118/191453_1_4.jpg" alt="e.JPG" />。

一個(gè)3層單輸入、單輸出、n個(gè)隱節(jié)點(diǎn)的BP網(wǎng)絡(luò)結(jié)構(gòu)如圖l所示。

評(píng)論