基于FPGA的自適應(yīng)鎖相環(huán)設(shè)計

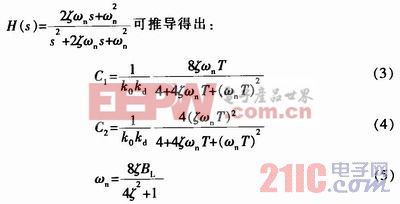

式中,ωn、T分別對應(yīng)鎖相環(huán)的自然角頻率和環(huán)路調(diào)整時間間隔,可根據(jù)系統(tǒng)要求進行取值,設(shè)計中取T為采樣時間間隔,即每個點調(diào)整一次,ζ取常用值 0.707,ko、kd分別對應(yīng)鑒相增益和相位控制靈敏度,BL表示環(huán)路噪聲等效帶寬。由式(3)~式(5)可知,噪聲等效噪聲帶寬BL和環(huán)路濾波器系數(shù) C1、C2一一對應(yīng),因此改變噪聲帶寬即可通過調(diào)整系數(shù)C1、C2實現(xiàn)。傳統(tǒng)鎖相環(huán)中,取固定值,一般選取滿足條件BL≤ O.1Rb的值,其中Rb為信息數(shù)據(jù)速率。

4.2 系數(shù)調(diào)整

相干解調(diào)系統(tǒng)中,同步系統(tǒng)的相位誤差直接影響著系統(tǒng)的誤碼性能,其對應(yīng)關(guān)系為:,其中ψ為相位誤差。因此噪聲水平較高時,應(yīng)該盡可能減小噪聲帶寬,近而減小ψ值,噪聲水平較低時,適當(dāng)增加噪聲帶寬,加快跟蹤速度。

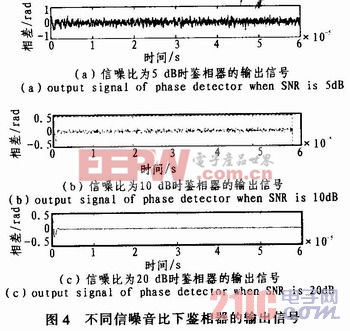

利用仿真軟件MATLAB對3種噪聲水平下的輸入信號進行相位跟蹤仿真,3種情況下,鎖相環(huán)參數(shù)相同,輸入的調(diào)制信號相同,不同的是對信號疊加3種功率不同的噪聲。結(jié)果顯示,鎖相環(huán)中引入的噪聲越大,則鑒相器模塊輸出信號的抖動越大。輸入信號的信噪比為5、10和20 dB時,鑒相器模塊的輸出信號如圖4所示。

由圖4可以看出,噪聲水平越高,則鑒相器的輸出信號抖動越厲害,于是設(shè)計中利用鑒相器輸出信號的抖動狀況來判斷鎖相環(huán)中的噪聲水平,并根據(jù)噪聲水平來調(diào)整 C1、C2值。MATLAB仿真結(jié)果顯示,鑒相器的輸出值是在0值上下浮動,因此利用FPGA實現(xiàn)此功能時,可利用鑒相器輸出值的絕對值或平方值判斷噪聲大小,浮動越大則噪聲水平越高。利用單個點的抖動來判斷時,具有一定的偶然性,結(jié)果不準(zhǔn)確,容易產(chǎn)生誤判,因此,在FPGA硬件板上利用VHDL編程實現(xiàn)時,對鑒相器的輸出數(shù)據(jù)取絕對值或進行平方處理,并對連續(xù)15個點的絕對值或平方值進行累加運算,利用累加的結(jié)果來判斷相位抖動的大小。對15個點取和時,利用樹形加法結(jié)構(gòu),引入流水線設(shè)計方法,使各個加法器并行工作,確保輸出結(jié)果的速率和輸入數(shù)據(jù)的速率相等。計算過程中使用絕對值代替平方值,能獲取與平方值相似的結(jié)果,有效降低運算量。進行帶寬調(diào)整時,可以利用當(dāng)前應(yīng)該設(shè)置的BL值計算出與之對應(yīng)的環(huán)路濾波器系數(shù)C1、C2由式(3)~式(5)可以看出,通過BL計算C1、C2時比較復(fù)雜,涉及多次除法運算、乘法運算以及加法運算,在FPGA中,實現(xiàn)除法器、乘法器都是比較占用邏輯資源的,因此設(shè)計中不采用直接計算的方法,而是利用查找表法來實現(xiàn),首先訂制2個容量為256的ROM,將可取的帶寬值平均劃分為256等分,對每個帶寬值對應(yīng)的C1、C2 值預(yù)先進行計算,計算結(jié)果經(jīng)量化處理后,以MIF文件的形式分別加載到ROM1、ROM2。ROM1、ROM2的地址線均為8位設(shè)計中連接到同一信號,對應(yīng)地址范圍為0x00到OxFF,由圖2中的噪聲評估模塊產(chǎn)生。噪聲評估模塊輸出的初始值設(shè)置為0x7F,即初始帶寬值設(shè)置為可取范圍段的中間值,之后根據(jù)噪聲評估模塊的結(jié)果,與提前設(shè)定的上限值、下限值進行比較,并根據(jù)比較結(jié)果調(diào)整帶寬值,其中上限值、下限值通過仿真得出,這兩個域值與FPGA實現(xiàn)時采用的位寬、位截短處理、濾波處理等有關(guān)。為防止過于頻繁地進行調(diào)整,程序中設(shè)定,如果連續(xù)3次的抖動高于上限值且當(dāng)前地址值大于Ox00,則減小帶寬值 (即地址減1),相反,若連續(xù)3次的抖動低于下限值且當(dāng)前地址值小于0xFF,則增加帶寬值(即地址加1)。

評論