基于FPGA的帶CRC校驗的異步串口通信

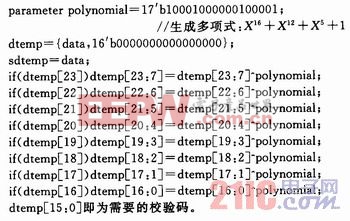

③CRC碼生成

循環冗余校驗(cyclic redundancy check,CRC)是一種在數據傳輸中廣泛應用的差錯檢測方法。CRC的設計思想是將數據包當作一個多位的二進制數,用這個二進制數除以一個選定的多項式,所得的余數作為校驗數據直接附加在數據后面發送出去,在接收端對數據除以相同的多項式如余數為零則表示沒有錯誤被檢測到。CRC的工作過程如下:假設需要發送的數據為8位,校驗多項式一般為X16+X12+X5+1。首先將發

送數據左移16位生成一個新的數列,然后采用模2運算(異或)將新數列除以校驗多項式,所得余數序列即為冗余循環碼,將其直接加到數據后面即可。

部分程序如下:

將生成CRC碼與接收到得CRC碼進行比較,判斷傳輸過程是否有誤,若無誤就將數據信息發送出去。

1.2.3 數據發送

數據發送部分的功能是將檢驗完畢后的正確數據發送出去,實際上是一個并/串轉換。當數據校驗正確后err置位,通過pos_err濾波檢測err的上升沿,上升沿到來時pos_err置高1個時鐘周期,此時開始進行數據發送。串口通信的傳輸格式是:1位起始位,8位數據為,1位停止位。所以需要將數據裝載成發送格式,然后再發送出去。發送時先發送起始位O,再發送數據低位,然后發送高位,最后在發送停止位1。這部分用計數器num進行計數,在case(num)語句塊里,分別發送這10位。

2 實驗驗證

按照以上設計方案編寫Verilog HDL程序,下載到FPGA芯片中,通過微機與設計系統的通信來驗證該設計方案的可行性與可靠性。下載程序前,事先連接電路,連接好電源、串口線、 Byteblaster下載電纜。程序代碼用開發軟件QuartusⅡ5.O下載到FPGA芯片里,具體操作步驟如下:

新建Verilog HDL文件→輸入并保存代碼→新建工程→設置選項(選擇目標芯片,本實驗用的是cyclone公司的EPlC6T144C8N,配置方式,下載方式等)→編譯→配置引腳→編譯→選擇下載電纜→下載運行。

按照以上步驟下載好程序即可以進行實驗驗證。微機串口調試助手的選項如下:波特率:96 000 b/s;校驗位:NONE;數據位:8位;停止位:1位;接收區設置:16進制顯示;發送端設置:16進制發送。

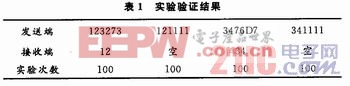

表1所示為實驗驗證結果,其中的12的CRC碼為3273,34的CRC碼是76D7。

實驗驗證結果可以看出,數據傳送的正確率很高。

3 結語

簡單介紹了FPGA芯片、Verilog HDL、串口通信協議以及硬件電路設計,詳細分析了軟件部分各個模塊的設計方法,并下載程序到FPGA芯片,通過微機與系統之間的串口通信,驗證了該設計的可行性與可靠性。在實現過程中,著重分析了移位串/并,并/串轉換過程,并加入CRC檢驗碼生成過程和具體校驗過程,用Verilog HDL語言編程,實現了串口通信的采集、數據處理、數據發送的全過程。該方案的特點是實現容易,速度快,效率高,實用性強,可以廣泛應用于終端、打印機、邏輯分析儀、磁盤等與計算機相距不遠的人-機交互設備和串行存儲的外部設備。

本文引用地址:http://www.104case.com/article/191423.htm

fpga相關文章:fpga是什么

通信相關文章:通信原理

評論