基于FPGA的帶CRC校驗的異步串口通信

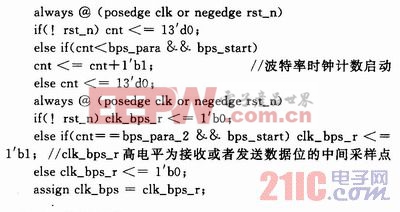

1.2.1 波特率設置

系統時鐘是由PFGA的16引腳輸入的24 MHz時鐘,而異步串口通信的波特率設置為9 600 b/s,所以需要對主頻進行分頻。分頻過程定義了2個常量,分別用來存儲波特率96 000 b/s的分頻計數最大值bpspara和分頻計數的一半bps_para_2。每個系統時鐘的上升沿來臨時計數器cnt加1,每bps_para_2個系統時鐘周期clk_bps改變1次狀態,這樣就產生了96 000 b/s的波特率。部分分頻代碼如下:

1.2.2 數據接收

數據接收模塊所要完成的任務包括:

(1)連續接收3個字節:1個字節的數據信息和2個字節的數據信息的CRC校驗碼;

(2)取出這3個字節的第一個字節,重新生成CRC碼;

(3)講新生成的CRC碼與接收到得CRC比較,若相同則傳輸過程中沒有出現錯誤;若不相同則傳輸過程有錯誤,等待接收下一組數據。

①單字節串/并轉換

串口通信發送數據的格式:1位起始位(低),8位數據位,1位停止位(高),共10位(這里沒有校驗位ParityBit)傳輸時的順序是:起始位+數據位低位---數據位高位+停止位,其時序圖如圖3所示;

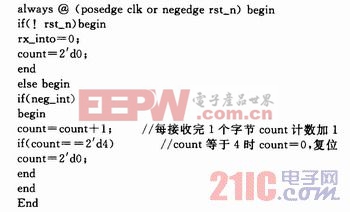

②3字節連續接收并儲存

為了連續接收3個字節數據,定義中斷寄存器neg_int和計數器count,復位時都清零,開始接收數據時rx_int置高,每接受完1個字節,rx_int清零,此時檢測rx_int的下降沿,下降沿到來時計數器count加1,直到接收完第3個字節時count的值是3。部分程序如下:

因為HDL是硬件描述語言,所以必須時刻檢測是否有起始位到來,需用幾個并行的always語句塊來處理。在接受完第1個字節后繼續檢測下降沿,并把接收到的數據暫存到寄存器data中,接收完第2個字節后仍繼續檢測下降沿,并暫存數據到crc16[15:8],接收完第3個字節繼續檢測下降沿,暫存數據到crc16[7:O]。等待下面的校驗處理。下面用case語句塊來暫存數據。

fpga相關文章:fpga是什么

通信相關文章:通信原理

評論