基于FPGA的帶CRC校驗的異步串口通信

摘要:由于FPGA具有速度快,效率高,靈活穩定,集成度高等優點,所以為了提高串口通信的速度和效率,在串行通信中采用FPGA來實現串口通信是十分必要的。由于通信傳輸的不確定性以及干擾等原因,串行通信經常會出現異常情況。然而,在串行通信中添加CRC校驗,可以提高通信的可靠性。采用Verilog HDL設計的一個帶CRC校驗的串口通信程序,對其下栽到FPGA芯片中進行實驗驗證,得到的結論是用FPGA進行串口通信,可大大提高通信的速度和效率,且CRC校驗確保了通信的準確性及卡可靠性。

關鍵詞:Verilog HDL;串口通信;FPGA;CRC檢驗

O 引言

現場可編程門陣列(field programmable gate array,FPGA)在數字電路設計中已經被廣泛使用。這種設計方式可以將以前需要多塊集成芯片的電路設計到一塊大模塊可編程邏輯器件中,大大減少了電路板的尺寸,增強了系統的可靠性和設計的靈活性。本文詳細介紹了已在實際項目中應用的基于FPGA的串口通信設計。硬件描述語言(hardware description language,HDL)是一種用形式化方法來描述數字電路和設計數字邏輯系統的語言。數字邏輯電路設計者可以利用這種語言來描述自己的設計思想,然后利用電子設計自化(EDA)工具進行仿真,再自動綜合到門級電路,然后用ASIC或Soft-Core實現其功能。Verilog HDL是硬件描述語言的一種,用于數字電子系統設計。串口通信是指在一個時間內傳輸1位數字數據。從19世紀的二進位電報編碼,發展到現在的RS 232(EIA 232),主要用于連接終端和大型主機。串口通信在過去的40年里,大大推動了通信技術的發展。通信協議是指通信雙方的一種約定。約定包括對數據格式、同步方式、傳送速度、傳送步驟、檢糾錯方式以及控制字符定義等問題做出統一規定,通信雙方必須共同遵守。因此,也叫通信控制規程,或稱傳輸控制規程,它屬于 ISO’sOSI七層

參考模型中的數據鏈路層,其主要完成的作用如下:

(1)實現數據格式化;

(2)進行串/并轉換;

(3)控制數據傳輸速率;

(4)進行錯誤檢測;

(5)進行TTL與EIA電平轉換;

(6)提供EIA-RS 232C接口標準所要求的信號線;

(7)為了完成上述串行接口的任務,串行通信接口電路一般由可編程的串行接口芯片、波特率發生器、EIA與TTL電平轉換器以及地址譯碼電路組成。

1 方案設計與分析

1.1 硬件電路

該方案的硬件電路設計包括:FPGA芯片、MAX3232,DB9。其硬件電路與微機通信的結構框圖如圖1所示。

1.2 軟件設計思想

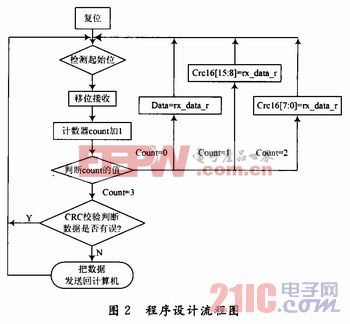

軟件部分的設計流程如圖2所示。

fpga相關文章:fpga是什么

通信相關文章:通信原理

評論