基于FPGA 與VHDL 的微型打印機的驅動設計

2. 2 軟件設計

軟件平臺采用A ltera 公司的FPGA 開發平臺Q uartus 。

Quartus 提供了一種與器件結構無關的設計環境,設計者不需要精通器件的內部結構,只需要運用自己熟悉的輸入工具( 如原理圖輸入或數字電路描述語言輸入) 進行設計,利用Quar tus 可以將這些設計轉換為最終結構所需要的格式。有關結構的詳細知識已寫入開發工具軟件,設計人員無需手工優化自己的設計。軟件的開發流程如圖4 所示。

圖4 軟件開發流程圖

使用VHDL 硬件描述語言來進行軟件設計。

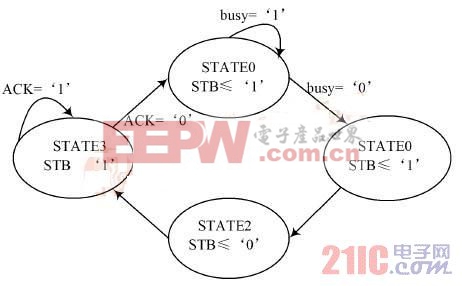

對微型打印機的驅動主要是對其工作時序進行正確的控制,利用VHDL 常見的狀態機來實現對打印機的工作時序的控制,根據時序圖1 所示的時序,狀態機使用4 個狀態,狀態轉換圖如圖5 所示。

初始狀態STA TE0 時,數據選通觸發脈沖信號STB 置“1” ( 高電平) ,檢測打印機是否正忙,如果打印機為空閑狀態( busy= “0”) ,轉入下一狀態STAT E1,否則( busy = “1 ” ) 繼續執行ST AT E0; 在狀態STAT E1,將數據寫入打印機,直接轉入下一狀態; 在狀態STAT E2,將數據選通觸發脈沖信號STB 置“0” ,打印機讀數據,轉入下一狀態; 在狀態ST ATE3,檢測數據是否已經被接受,若數據已被接受( ACK = “0” ) ,打印機轉入初始狀態ST AT E0,等待接受新數據,若數據未被接受( ACK = “1” ) ,繼續執行STAT E3 直到數據被接受。

圖5 狀態轉換圖

3 結 語

使用FPGA 與V HDL 硬件描述語言設計的微型打印機驅動,通過系統調試能夠完成對打印機的時序控制,目前已經在某型測試儀中正常使用。該設計系統控制簡單,抗干擾性強,可靠性高,移植性較好,能夠用于任何使用FPGA 芯片的系統中,具有一定的應用前景。

評論