基于FPGA 與VHDL 的微型打印機的驅動設計

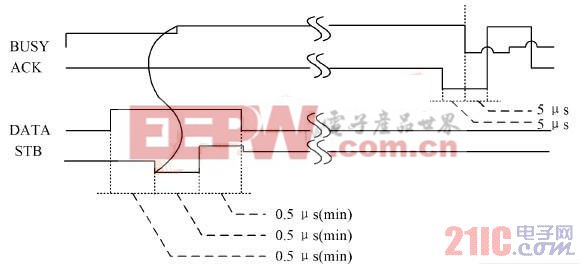

對打印機的驅動主要是對其工作時序進行正確的控制,RD DH 型并行接口定時圖如圖2 所示。本文引用地址:http://www.104case.com/article/191316.htm

圖2 并行接口定時圖

2 總體系統設計

使用Altera 公司的Cyclon ?系列的FPGA 芯片EP3C25Q240C8N 實現對RD DH 型微型打印機的硬件電路控制,使用Quar tus 開發工具,通過VHDL 語言實現對微型打印機的軟件功能實現。

2. 1 硬件電路設計

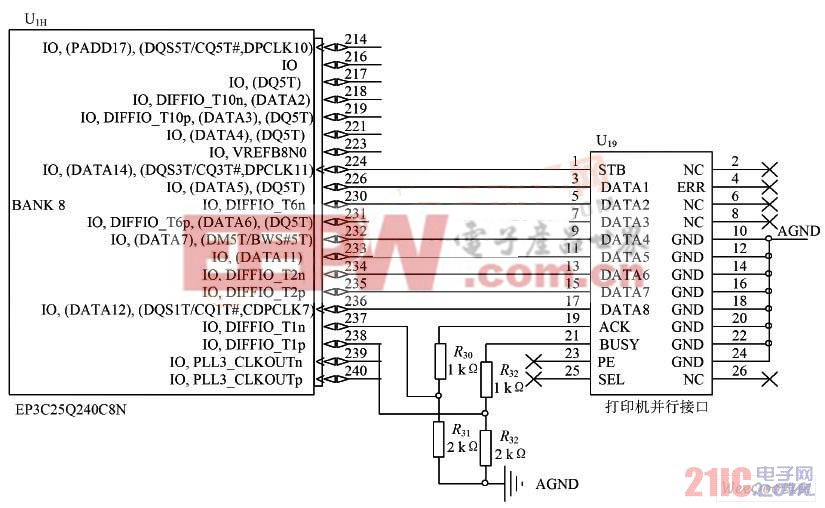

如圖3 所示為打印機與FPGA 的連接示意圖。

DATA 1~ DATA8 表示打印機的8 個數據位,他們的邏輯“1”表示高電平,邏輯“0”表示低電平; STB 為數據選通觸發脈沖,下降沿時讀入數據; ACK 為回答脈沖,低電平表示數據已被接受; BUSY 為高電平時表示打印機正忙,此時不接收數據。

由于 ACK 和BUSY 輸出的是5 V 的TT L 電平,而FPGA 的I/ O 口標準為3. 3 V LVCMOS 電平,因此這兩個信號作為FPGA 的輸入信號時,要進行分壓,保證電路正常運行。

圖3 FPGA 與打印機連接示意圖

評論