一種基于FPGA 的嵌入式塊SRAM 的設(shè)計(jì)

摘 要:文章中提出了一種應(yīng)用于FPGA 的嵌入式可配置雙端口的塊存儲(chǔ)器。該存儲(chǔ)器包括與其他電路的布線接口、可配置邏輯、可配置譯碼、高速讀寫電路。在編程狀態(tài)下,可對(duì)所有存儲(chǔ)單元進(jìn)行清零,且編程后為兩端口獨(dú)立的雙端存儲(chǔ)器。當(dāng)與FPGA 其他邏輯塊編程連接時(shí),能實(shí)現(xiàn)FIFO 等功能。基于2.5V 電源電壓、chart 0.22 μm CMOS 單多晶五鋁工藝設(shè)計(jì)生產(chǎn),流片結(jié)果表明滿足最高工作頻率200MHz,可實(shí)現(xiàn)不同位數(shù)存儲(chǔ)器功能。

本文引用地址:http://www.104case.com/article/191314.htm1 引言

對(duì)于邏輯芯片的嵌入存儲(chǔ)器來說,嵌入式SRAM 是最常用的一種,其典型的應(yīng)用包括片上緩沖器、高速緩沖存儲(chǔ)器、寄存器堆等。除非用到某些特殊的結(jié)構(gòu),標(biāo)準(zhǔn)的六管單元(6T)SRAM 對(duì)于邏輯工藝有著很好的兼容性。對(duì)于小于2Mb 存儲(chǔ)器的應(yīng)用,嵌入式SRAM 可能有更好的成本效率并通常首先考慮。

Xilinx 公司SRAM型FPGA 主要由配置存儲(chǔ)器、布線資源、可編程I/O、可編程邏輯單元CLB、塊存儲(chǔ)器BRAM 和數(shù)字時(shí)鐘管理模塊組成。它包含了分布式RAM,位于CLB中。每個(gè)CLB包含了16 × 1bit的SRAM結(jié)構(gòu)。BRAM的加入既增加了RAM的容量,也可構(gòu)成大型LUT,更完善了CLB 的功能。

2 BRAM塊劃分

現(xiàn)代數(shù)字系統(tǒng)對(duì)存儲(chǔ)器容量的存儲(chǔ)速率要求越來越高,讀訪問時(shí)間就是一個(gè)重要參數(shù),它是從地址信號(hào)的出現(xiàn)到存儲(chǔ)在該地址上的數(shù)據(jù)在輸出端出現(xiàn)的時(shí)間延遲。提高BRAM 讀取速度的一個(gè)有效辦法是減小位線和字線上的總負(fù)載電容,這可以通過減少連接在同一字線和位線上的存儲(chǔ)單元數(shù)目來實(shí)現(xiàn),即采用存儲(chǔ)陣列分塊技術(shù)。本電路采用設(shè)計(jì)多個(gè)BRAM的方法,每個(gè)BRAM都有自己的譯碼電路、敏感放大器和數(shù)據(jù)通道,各個(gè)BRAM 獨(dú)立工作,每個(gè)BRAM 的讀取時(shí)間得到了大大提高。

3 BRAM塊設(shè)計(jì)

3.1 BRAM與布線資源接口

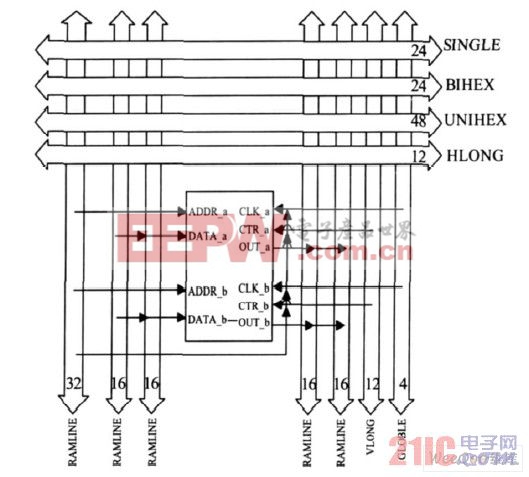

FPGA 中每個(gè)BRAM塊都嵌在內(nèi)部連線結(jié)構(gòu)中,與BRAM 直接相連的有RAMLINE、VLONG 和GLOBAL。左邊32根RAMLINE提供BRAM的地址輸入,也可以提供控制信號(hào)(CLK、WE、ENA、RST)的輸入。左邊兩組16 根RAMLINE 一起布線提供BRAM雙端口的數(shù)據(jù)輸入,右邊兩組RAMLINE提供BRAM雙端口數(shù)據(jù)輸出通道。4 根GLOBLE全局時(shí)鐘線優(yōu)化用作時(shí)鐘輸入,提供較短的延遲和最小的失真。VLONG也被專門用作BRAM中WE、ENA、RST的控制輸入。RAMLINE 為BRAM專有布線,如從水平方向的SINGLE、UNIHEX、BIHEX通過可編程開關(guān)矩陣PSM 把信號(hào)輸送到RAMLINE 上,進(jìn)而送到BRAM 用作地址、數(shù)據(jù)。而BRAM 的輸出也通過RAMLINE最終送到HLONG上。

圖1 BRAM周圍布線

相鄰BRAM 的RAMLINE 也可通過三態(tài)門連到下一級(jí)的RAMLINE,于是整列中的BRAM 可共享RAMLINE 上的數(shù)據(jù)。每個(gè)BRAM與FPGA其他電路的相連主要通過水平方向的4 組主要互連線完成。

3.2 BRAM內(nèi)部設(shè)計(jì)

BRAM為真正的雙端口RAM,兩個(gè)端口完全獨(dú)立,每個(gè)端口可以配置為讀寫端口,并可以把BRAM配置成特定的數(shù)據(jù)寬度。

linux操作系統(tǒng)文章專題:linux操作系統(tǒng)詳解(linux不再難懂)

評(píng)論