基于FPGA的IRTG-B碼編解碼器的設計與實現

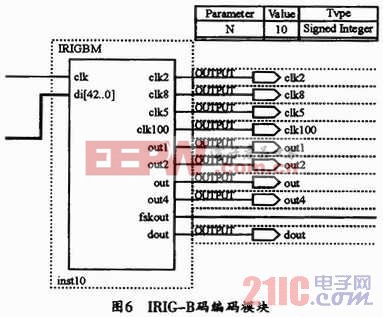

一般每個IRIG-B碼都包含有豐富的碼信息。它必須包含幀開始標志位、位置識別標志和索引標志,以使接受方能進行數據卸載,或通過位置識別標志和索引標志識別出相應的天、時、分、秒等信息。圖6所示是IRIG-B碼編碼模塊的設計圖。本文引用地址:http://www.104case.com/article/191278.htm

3 IRRIG-B解碼模塊設計

3.1 鎖相環PLL模塊

PLL鎖相環模塊用于實現系統同步功能,以使外部信號脈沖和提供的標準時鐘脈沖相位同步,從而實現輸入信號頻率對標準信號頻率的自動跟蹤。PLL主要由鑒相器(PD)、環路濾波器(LPF)和壓控振蕩器(VCO)等三個基本部件組成。本文選用Ouartus II軟件中宏功能庫中自帶的PIX模塊來實現其相位同步功能。

3.2 IRIG-B解碼模塊

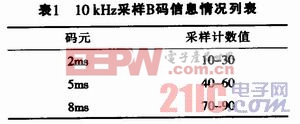

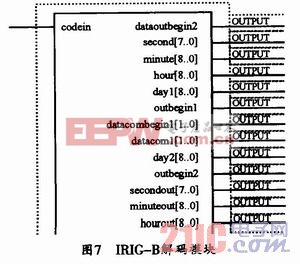

對IRIG-B碼進行解碼就是將B中包含的標準時間信號和天、時、分、秒信息提取出來。解碼的關鍵在于判別IRIG-B碼的幀開始標志位和相應的秒、時、分、天的位置和信息。通過檢測B碼中各個碼元的寬度(高電平),可以判斷相應的時間信息。該模塊可完成對IRIG-B碼的寬度檢測。如果寬度為8,則確定是位置識別標志,如果檢測到兩個連續的寬度都是8,第二個寬度為8的脈沖則作為幀開始標志位。如果寬度為5,則對應的數值為“1”,如果寬度為2,則對應的數值為“0”。

本設計采用10 kHz基準信號來采樣IRIG-B碼信號以提取碼元相關信息。由于10kHz與外部頻率脈沖不能完全同步,有一定時間誤差。所以,利用10 kHz脈沖信號來采樣B碼信號,可使三種碼元不會出現重疊,從而可以提高采樣精度。在捕獲方式下,當滿足捕獲條件時,硬件可自動將計數器中的數據寫入存儲器中,當B碼信號的上升沿到來時,計數器開始計數,下降沿到來時則停止計數,并通過采樣計數數值范圍來判斷對應的碼元,從而將直流碼解出。表1所列是用10kHz采樣B碼的信息表,圖7所示是IRIG-B解碼模塊示意圖。

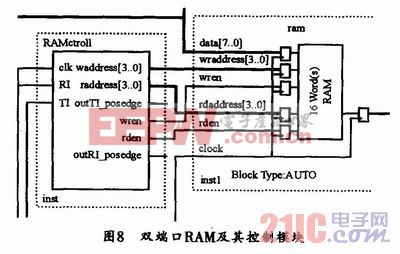

3.3 雙端口RAM和控制模塊

本系統中的RAM模塊主要完成時間信息的存儲,RAM通過讀寫控制信號來進行讀寫控制。當讀寫信號為高電平時進行寫操作,此時可以通過寫地址線控制把數據存儲到相應的存儲單元中;為低電平時則進行讀操作,此時可通過讀地址線控制把相應存儲單元的數據讀出。從而完成整個數據存儲的讀取,圖8所示是該雙端口RAM和控制模塊的示意圖。

4 結束語

基于FPGA的IRIG-B碼編解碼器有利于硬件電路的簡化并縮短開發周期,同時其工作穩定,可靠性高,可提供精確時間信息,在工程實踐中得到日益廣泛的應用。本系統采用模塊化設計,其系統的各個模塊之間有較好的關聯性,又有一定的獨立性,便于后期對系統功能的擴展。當以串行方式進行數據傳輸,用一個I/O端口即可完成數據的接收和發送,因而既節省系統資源,又可解決并行傳輸通道之間的相互干擾問題。

評論