基于FPGA的IRTG-B碼編解碼器的設計與實現

2 IRIG-B編碼模塊的設計

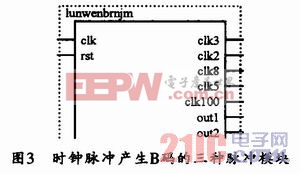

2.1 時鐘脈沖產生模塊設計

為了達到系統所要求的精度,使頻率較為穩定,設計時可用更高的頻率作為時鐘分頻鏈的第一主時鐘。這里采用鎖相環實現倍頻方法來提供所需的頻率,可選用Quartus II軟件中宏功能庫中自帶的PLL來提高整體的運算速度,同時也能合理的進行資源綜合。實事上,使用基本的宏定義模塊可以明顯地提高用戶的設計開發時間。時鐘脈沖產生電路是IRIG-B碼產生器不可缺少的單元,該電路主要由幾個分頻器級聯和一些邏輯門組成。

電路中的數字分頻器可對外部提供的頻率進行分頻,以產生系統所需時序脈沖和B碼的三種基本編碼形式脈沖,其寬度(高電平)分別為2ms、5 ms、8 ms,頻率為100Hz的脈沖信號:其中第一種是高電平為2 ms、低電平為8 ms的脈沖(代表邏輯“0”);第二種是高、低電平均為5 ms的脈沖(代表邏輯“1”);第三種是高電平為8ms、低電平為2 ms的脈沖(作為位置識別標志和參考碼元)。Quartus II軟件下的仿真模塊結果如圖3所示。本文引用地址:http://www.104case.com/article/191278.htm

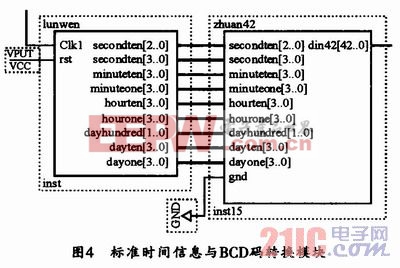

2.2 標準時間信息和BCD碼轉換模塊設計

該模塊由百分秒計數器、秒計數器、分計數器、時計數器和天計數器級連而成。它可對預置的時間進行秒加一,每隔一秒對時間信息刷新一次,從而形成動態BCD碼,并使時間信息符合IRIG-B碼的格式。標準時間信息和BCD碼轉換模塊如圖4所示。

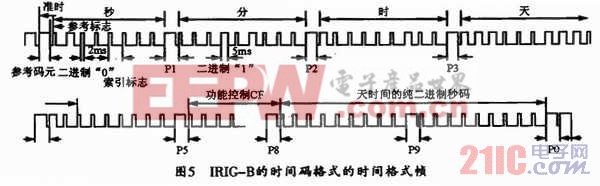

2.3 IRIG-B碼DC格式的生成

IRIG-B(DC)時間碼格式的時間格式幀從幀參考標志開始,因此,連續兩個8ms寬脈沖中的第二個8ms脈沖的前沿為秒的準時點,該點標志著一個時間格式幀的開始,稱為參考碼元。從第二個8ms開始,分別為第1、2、…、99、0個碼元。B碼時間格式中含有秒、分、時、天等信息,其位置在P0~P5間。時間信息中,高電平用5ms脈沖表示,低電平用2 ms脈沖表示,其中秒信息占用第2、3、4、5、7、8、9碼元;分信息占用第11、12、13、14、16、17碼元;時信息占用第20、21、22、24、26、27碼元;天信息占用第31、32、33、34、36、37、38、38、41、42碼元;P6~P10包含其他控制信息(這里沒有應用)。另外,第6、15、25、35、…、95碼元為索引標志,用2ms脈沖寬度表示,固定為“0”。時、分、秒均用相應BCD碼表示,低位在前,高位在后,個位在前,十位、百位在后。圖5所示是IRIG-B時間碼的格式幀示意圖。

評論