基于FPGA的IRTG-B碼編解碼器的設計與實現

摘要:為提高整個系統時間的同步精度,以便為測量設備提供可靠的時間信息和標準頻率信號,給出了一種基于FPGA的IRIG-B編解碼器的設計與實現方法。新系統基于模塊化設計,其中編碼部分完成標準時間信息及相應的BCD碼的產生,并在標準時間BCD碼中加入幀開始標志位、位置識別標志和索引標志識別,從而將BCD格式的時間信息變成IRIG-B格式碼,同時數據并串處理可通過FPGA的一個I/O端口發送串行數據。解碼部分則完成串行IRIG-B格式碼的接收并判斷幀開始標志位和位置識別標志,再解出相應原始時間信息并存儲到雙端口的RAM中,最后以并行方式輸出。

關鍵詞:IRIG-B;可編程邏輯器件;FPGA;編碼器;解碼器

0 引言

時間統一(以下簡稱時統)系統是武器系統試驗測試、通信、氣象、航天、工業控制、電力系統測量與保護等領域的關鍵技術,主要為其他參試測試設備提供標準時間信號和標準頻率信號。隨著現代信息技術的不斷發展,對標準化時間系統設備的要求越來越高,IRIG-B碼以其優越性成為時間系統設備的首選。而對信號的幀結構的可編程度、集成度的需求越來越高,用于時間系統的IRIG-B碼源的設計也趨于高度集成化。FPGA可編程邏輯器件的規模比較大,適合于時序、組合等邏輯電路應用場合,同時具有實時性好、可靠性高、成本低、可編程等優勢。本文介紹了采用Ahera公司的EP20K200E器件所設計的IRIG-B時統信號發生及解碼電路。

IRIG-B編碼模塊主要利用外部時鐘脈沖信號來觸發,它將用于產生IRIG-B碼的各種門電路集成在一個芯片,以產生標準的IRIG-B串行時間碼并向設備終端發送,從而完成DC碼編碼。通過設備終端對接收到的IRIG-B碼進行解調,便能產生出系統所需的標準時間和各種控制信號,然后再存儲到相應的雙端口RAM中。

1 系統整體硬件設計

IRIG(Inter-Range Instrumentation Group)是美國靶場司令部委員會的下屬機構,稱為“靶場時間組”。IRIG-B碼(DC)以其實際的優越性能而成為時統設備最佳選擇的標準碼型。IRIG時間標準有兩大類:一類是并行時間碼格式,這類碼由于是并行格式,傳輸距離較近,且是二進制,因此遠不如串行格式廣泛;另一類是串行時間碼,共有六種格式,即A、B、D、E、G、H。它們的主要差別是時間碼的幀速率不同,B碼的主要特點是時幀速率為1幀/s;而且攜帶信息量大,經譯碼后可獲得1、10、100、1000 c/s的脈沖信號和BCD編碼的時間信息及控制功能信息;此外,B碼的分辨率高,調制后的B碼帶寬能適用于遠距離傳輸,它分為直流、交流兩種,而且接口標準化,國際通用。

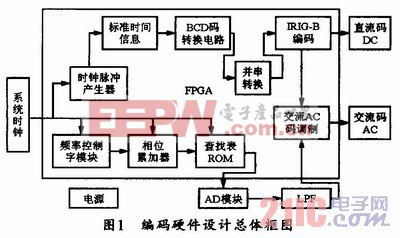

IRIG-B碼編碼器由時鐘脈沖發生器模塊、標準時間形成模塊、BCD碼轉換模塊、并串轉換、直流碼形成模塊和交流碼模塊組成,其編碼器硬件設計總體框圖如圖1所示。

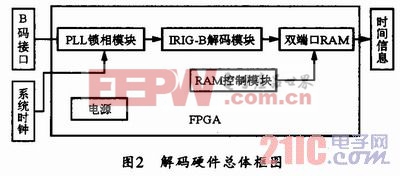

IRIG-B解碼器則由鎖相環PLL模塊、IRIG-B解碼模塊、雙端口RAM、RAM控制模塊等組成。其解碼硬件的設計框圖如圖2所示。

評論