基于HyperLynx的FPGA系統信號完整性仿真分析

4.2.1 時鐘信號的端接

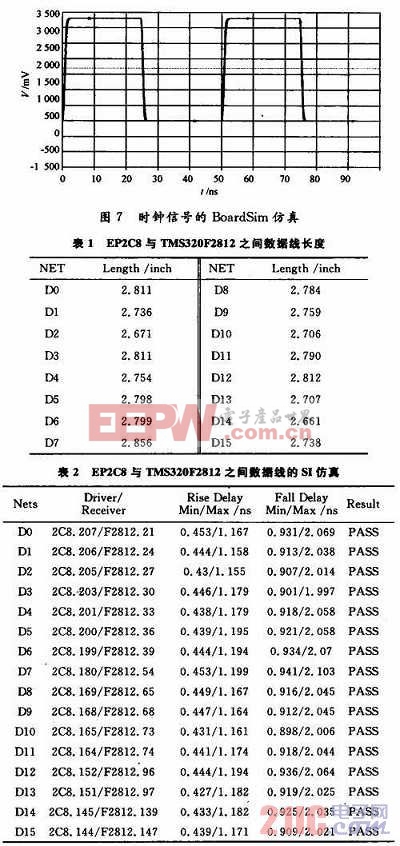

時鐘信號網絡標號為CLKIN,端接電阻阻值是51 Ω,SI仿真的結果如圖7所示,可見BoardSim仿真與在LineSim中的仿真相差無幾,滿足SI要求。本文引用地址:http://www.104case.com/article/191200.htm

4.2.2 數據線的端接

雖然用蛇行線可以解決信號的時序問題,但要注意的是蛇形線對信號完整性有一定影響。蛇行線的間距越小、耦合長度越長,則信號的串擾也越大,因此設計時需要注意這一點。表1是EP2C8與TMS320F2812之間的D0~D15這16根數據線長度,最短的網絡是D14只有2.661inch,最長的是D7有2.856 inch,長度變化控制在(2.76±0.1)inch之內。SI仿真結果見表2。

表2為BoardSim對數據線SI批量仿真結果。從中發現16根數據線的上升和下降沿的具體時延基本相當,說明通過正確端接和等長線保證了信號接收端的質量和時延等要求。接著對這幾根數據線進行批量的EMC仿真,仿真設定的標準是FCC和CISPR,結果為Net's EMCis within selected limits,可知系統滿足EMC要求。

5 結語

本文利用HyperLyn軟件和元器件的IBIS模型對TMS320F2812和EP2C8系統進行了信號完整性仿真分析。通過分析可知,合適的端接電阻可以大大減小信號在導線上的反射和串擾。采用蛇形線的走線方案解決了高速數據線的時延問題,走線長度匹配后的數據線在上升/下降沿的具體時間基本相當,滿足SI要求。

評論