基于HyperLynx的FPGA系統(tǒng)信號完整性仿真分析

串擾是信號完整性問題之一,它是指有害信號從一個網(wǎng)絡轉(zhuǎn)移到相鄰網(wǎng)絡。串擾可分為近端串擾(NEXT)和遠端串擾(FEXT),傳輸線的反射跟串擾也有聯(lián)系,采用合適的源端端接和遠端端接可以在一定程度上減小串擾。但串擾與信號之間的容性耦合和感性耦合有關,串擾不可能完全消除,只能減小。在TMS320F2812和EP2C8之間有大量的高速數(shù)據(jù)線,如果不進行處理則有可能接收錯誤的數(shù)據(jù)。圖4所示為用LineSim對數(shù)據(jù)線D8,D9和D10進行SI仿真的結果,設定D9是被干擾的網(wǎng)絡,D8、D10是攻擊網(wǎng)絡,振蕩頻率為20 MHz,端接電阻為50 Ω。從圖可知D9受到的干擾較小,過沖電壓只有122 mV。如果想要進一步減小串擾則可以減小走線寬度到8 mil,同時縮短走線耦合長度。本文引用地址:http://www.104case.com/article/191200.htm

3.2 高速信號線時序問題

TMS320F2812和EP2C8之間數(shù)據(jù)收發(fā)率高,因此時序就變得十分重要,如果兩信號到達接收端的時差近似于一個采集周期將導致接收到錯誤的數(shù)據(jù)。為了避免這種時序可題的發(fā)生,通過蛇形線來保證高速信號走線長度的一致,如圖5所示。PCB設計的工具是Altium公司的DXP 2004。

4 BoardSim仿真

BoardSim是在PCB繪制完成后進行的仿真,生成整版報告,驗證原有設計的合理性、修正布局布線。仿真將利用器件的IBIS模型對已經(jīng)設計好的PCB走線進行仿真,包括信號完整性、EMC、時序等。

4.1 串擾仿真驗證

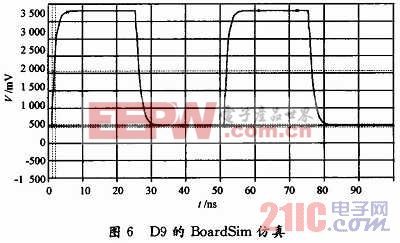

第3.1節(jié)中已經(jīng)對D8,D9和D10進行了串擾仿真,現(xiàn)在用BoardSim來驗證上述仿真結果。考慮到實際電阻值沒有50 Ω,所以采用端接電阻值為51 Ω,振蕩頻率為20 MHz。圖6所示為當D8,D10有數(shù)據(jù)通信時D9受到的干擾。由圖可知,D9處的波形抖動很小,串擾電壓過沖只有44.8 mV,下沖電壓只有-39.8 mV,基本上不會影響D9的信號,結果表明已經(jīng)通過信號完整性檢查。

4.2 端接仿真驗證

主要驗證時鐘信號和數(shù)據(jù)線的端接方案的合理性。

評論