基于HyperLynx的FPGA系統信號完整性仿真分析

摘要:針對目前高速電路發展帶來的信號完整性問題,在分析信號完整性要求的基礎上,借助HyperLynx仿真軟件,通過器件IBIS模型,對基于EP2C8和TMS320F2812組成的系統進行信號完整性分析和仿真。基于反射原理來介紹減少反射的端接方法,利用大量的板前和板后仿真對設計方案進行反復驗證。研究結果表明,HyperLynx可以解決該系統信號完整性方面存在的諸多問題,仿真結果給實際工程提供了借鑒。

關鍵詞:信號完整性;可編程邏輯器件;HyperLynx;IBIS模型

0 引言

隨著高速電路的不斷發展,時鐘頻率早已進入吉赫茲時代,電路板尺寸的減小、設備集成度的提高,使得信號完整性問題變得越來越重要。當時鐘頻率超過100 MHz時,如果不滿足系統的信號完整性要求,可能導致系統工作不穩定,同時也會帶來EMC問題。隨著FPGA和DSP處理速度的提高,帶來的信號完整性問題日益嚴重,這需要電子工程師重點考慮。

目前,有很大一部分文章從理論上分析信號完整性,而從實際應用方面分析的文章較少。基于此,本文主要研究通過對EP2C8和TMS320F2 812組成的系統所涉及的仿真問題進行了分析和研究,通過對關鍵信號線的仿真來分析系統的信號完整性。

1 HyperLynx軟件

HyperLynx是Mentor Graphics公司推出的高速仿真工具,從內容上可分為信號完整性仿真(SI)、電源完整性仿真(PI)和電磁兼容性仿真(EMC);從結構上可分為板前仿真(LineSim)和板后仿真(BoardSim)。為了保證PCB設計的成功率,在設計前遵守一些良好的設計規則很重要。HyperLynx軟件則提供了一個驗證設計方法和檢測PCB性能的環境,這將會提高工作效率。

2 面向系統的信號完整性仿真分析

2.1 系統構成和關鍵信號

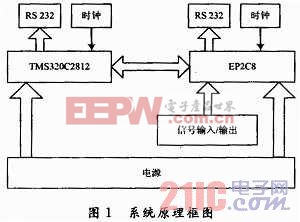

TMS320F2812和EP2C8構成的系統原理框圖如圖1所示。

由于系統信號線眾多,如果全部對它們進行仿真,將會花費很大的時間,只需對茨鍵信號仿真。根據器件上升沿、工作頻率、走線長度、時鐘信號等作為劃分關鍵信號的條件。明確了高速信號有TMS320F2812和EP2C8的通信端口、時鐘網絡、EP2C8數據接收端等。這些高速信號易受干擾同時又容易干擾其他網絡,需要著重考慮這些信號線的設計。通過HyperLynx的仿真可以優化這些走線,找到合適的設計方法。

2.2 系統板層設計

在對系統仿真前,需要確定PCB疊層數、走線特性阻抗等,這是系統進行信號完整性仿真的基礎。對于微帶線,IPC推薦的特性阻抗近似式為:

![]()

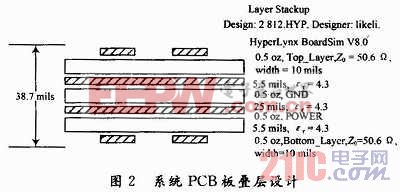

式中:h是導線離參考層的距離;w是導線寬度;t是導線厚度;由上式可知當w=2h時,走線特性阻抗為50 Ω,這可以作為經驗公式。該系統采用4層電路板,相對介電常數εr為4.3的FR4材料,走線特性阻抗設定為50 Ω,PCB板的厚度是1 mm,具體疊層方案如圖2所示。

評論