FSK/PSK調制的FPGA實現

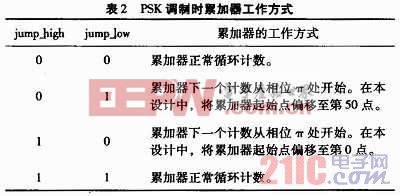

本設計中,取K=1,N=8,波形存儲深度為100個采樣點,則可得f0=fc/100。jump_high、jump_low、mode和clk通過控制相位累加器的輸出來實現:FSK/PSK波形合成輸出。當mode為低電平時,即FSK調制模式時,jump_high和jump_low中任一信號出現高脈沖時,累加器清零,然后根據clk進行循環累加。當mode為高電平時,即PSK調制模式時,累加器的工作方式如表2所示。本文引用地址:http://www.104case.com/article/191198.htm

ROM表是對選取的采樣點進行量化、編碼,通過相位累加器的地址值查找ROM表中的內容,以得到可合成正弦波的正弦點的值。其原理是:在橫軸上取100個采樣點,將縱軸的正弦值[-1,+1]總體提升一個單位,即將正弦值的取值區間變為[0,2],并將其均勻地分成255個量化區間,再對這255個量化間隔在00000000~11111111進行編碼,即將所取的采樣點的幅度值對應到各個量化間隔。

具體實現方法,可通過用Matlab產生一個mif文件。Matlab源程序如下:

3 系統仿真結果

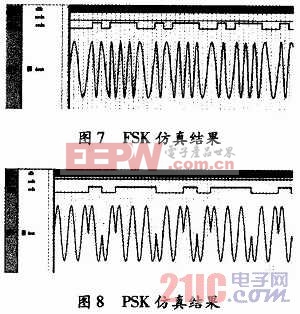

Altera公司的QuanusⅡ集合了綜合和仿真的功能。本設計在Quartus II中完成了VHDL的代碼編寫和綜合布線,并對整個設計系統進行了時序仿真,仿真結果如圖7~圖8所示。其中,clk為外接輸入100 MHz時鐘;mode為模式控制鍵;code為由m序列產生的偽隨機碼,用做基帶碼元;dout為輸出的調制結果。

圖7中,mode的值為“0”,說明是FSK調制方式。從圖中可以看出,當基帶碼元code為“0”時,dout輸出低頻調制波。當基帶碼元code為“1”時,dout輸出高頻調制波。實現了用不同的頻率變化傳遞數字信息,完成了FSK調制。

圖8中,mode的值為“1”,說明是PSK調制方式。從圖中可以看出,dout的輸出波形頻率是單一的,當基帶碼元由“1”向“0”跳變時,波形出現倒π現象,實現了通過相位變化傳遞信息,完成了PSK調制。

4 結束語

介紹了一種基于DDS技術的FSK/PSK調制方式的FPGA實現方法。整個系統采用VHDL硬件描述語言進行軟件編寫,參數修改方便,并具有較強的可移植性。其原理簡單,易于實現。相比傳統模擬調制方式,這種數字調制方式具有較好的穩定性和抗干擾能力,在通信領域中具有較強的實用性。

評論