FSK/PSK調制的FPGA實現

2.1 分頻器

分頻器對頻率為f0的時鐘輸入信號clk分別以分頻系數D1,D2和D3產生FSK/PSK調制器和m序列的基準時鐘信號f1,f2和f3。其關系如式(1)所示。

f1和f2決定了FSK調制信號的兩個載波頻率,f2決定了PSK調制信號的載波頻率,f3決定了基帶碼元速率。為了保證每個基帶碼元的寬度T是載波周期的整數倍,在選擇分頻系數時應滿足式(2)。

式中,M為D1和D2的最小公倍數。

2.2 m序列產生器

m序列是由多級移位寄存器或其他延遲元件通過線性反饋產生的最長的碼序列。m序列的最大長度取決于移位寄存器的級數,而碼的結構取決于反饋抽頭的位置和數量。其特點是:隨機特性、預先可確定性、循環特性。

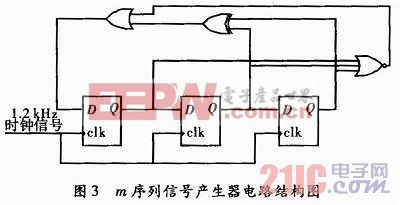

本設計利用帶有兩個反饋抽頭的3級反饋移位寄存器得到一串7位循環序列“1110010”,并采取措施防止進入全“0”狀態。通過更換時鐘頻率,可以方便地改變輸入碼元的速率。這一系列的循環序列碼作為基帶信號碼元。其電路結構如圖3所示。本文引用地址:http://www.104case.com/article/191198.htm

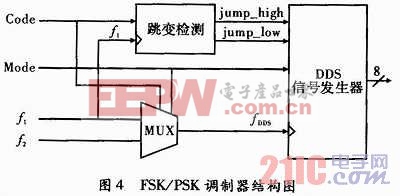

2.3 FSK/PSK調制器

FSK/PSK調制器由時鐘選擇模塊、跳變檢測模塊和DDS信號發生模塊3部分組成。原理如圖4所示。

評論