降低CPLD的功耗的嵌入式應用

2.5 選擇邏輯門

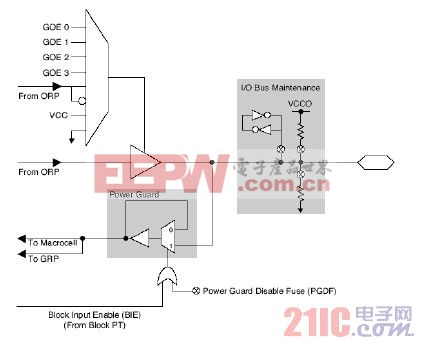

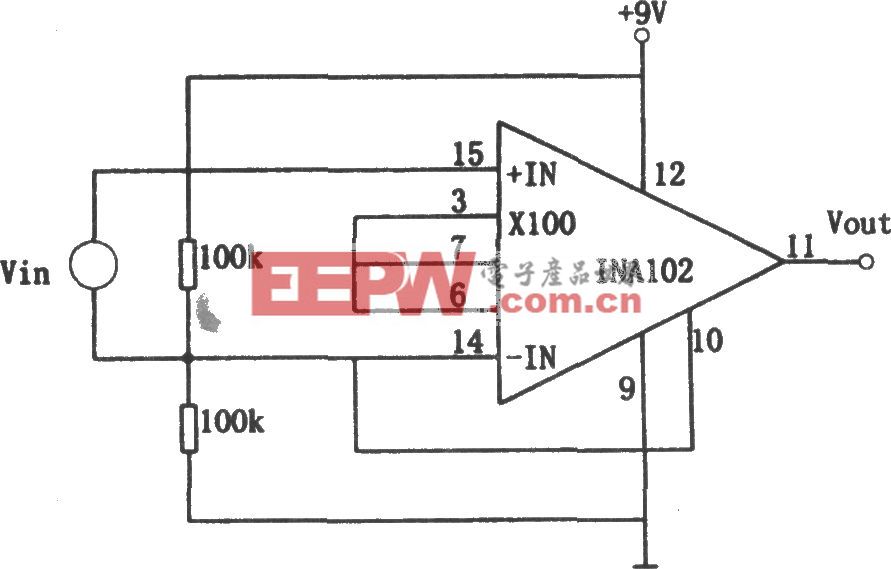

如同大多數的CPLD,ispMACH 4000ZE具有一個功能(萊迪思稱為“Power Guard” 功耗衛士),當它們不需要相關的邏輯時,可禁用單獨的輸入。主機處理器、其他的外部邏輯,或CPLD的其他部分可以使用器件的塊輸入使能線,以保持CPLD的邏輯選定的塊被時鐘控制(圖4)。例如,如果CPLD的某個部分被用作解碼器電路,只有該功能正在使用時,主處理器可以使它能工作,使之能夠在其余的時間保持休眠狀態。

圖4 Power Guard電路

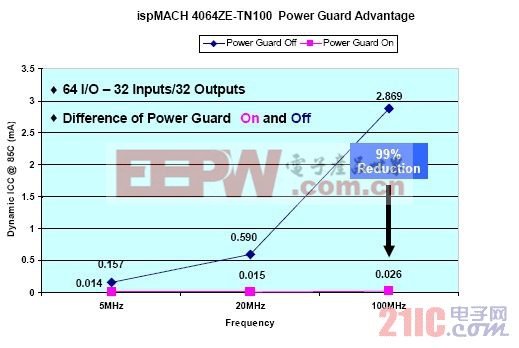

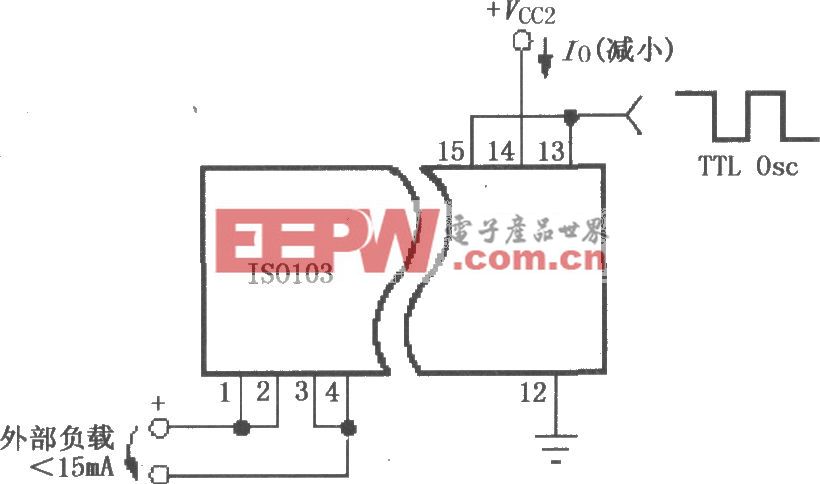

根據實際的應用使用Lattice的Power Guard或其他方法來禁用時鐘至選定的CPLD的輸入引腳,這樣可以大大降低動態功耗。尤其是如果邏輯信號的時鐘頻率超過30兆赫時,這些方法特別有用。圖5說明了可以用選擇邏輯時鐘技術實現潛在的節省功耗的方法。

圖5 Power Guard 節省的功耗

3 針對低功耗的I/O設計

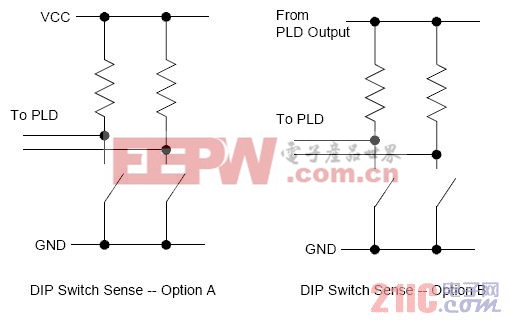

除了使用已經闡述的技術,目前大部分項目給予精明的工程師更多節省多余的微瓦功耗的機會-如果他們愿意關注潛伏在許多設計中的微小能源汲取部分。一個好的例子是無處不在的為開關提供讀出電壓的上拉電阻,以及連接到CPLD的輸入線(圖6)。通過使用CPLD的輸出,或其他控制線至電源電壓到讀出線,只有當他們被讀取時,并且讀出線接地時,設計人員方可去除這個小而穩定的電流。

圖6 無源和有源功率開關讀出線

4 結語

大多數基于CPLD設計至少包括一些未引起注意的角落,在這些地方潛伏著耗能大戶,他們悄悄地汲取電池的能量。幸運的是,認真實施一些重要的原則可以制止這些討厭的寄生部分。當選擇CPLD和其他元件時,注意其靜態和動態功耗等級:他們隨供電電壓、溫度和工作頻率而變化。同樣要注意“最小”、“最大”和“典型“功耗指標,它們將影響你的設計。盡量減少CPLD的偏置電流,確保其待機配置不與其他與之相連的器件相沖突,關閉任何不必要的內部功能。

管理動態功耗,只給當前CPLD需要的部分加時鐘。萊迪思的Power Guard功能提供一個簡單的方法來選擇關閉時鐘至專門的輸入,如果無法使用的話,還有其他的技術可用。使用精確的電源控制驅動邏輯,可實現節省額外的動態功耗,使用盡可能低的電源電壓。檢查I/O的連接,看看是否有不必要的可去除的加載的汲取功耗的上拉/下拉電阻,或只在需要時才選擇加載電阻。

如果你仔細地將這些工具應用到下一個項目,設計中就不會有隱藏的汲取功耗的大戶,你的產品將會有很長的壽命哦!

評論