基于CPLD/FPGA的USB讀寫控制器

引言

隨著計算機科技的發展,無紙辦公日益成為各單位日常辦公的主要形式。而隨著USB存儲設備日益廣泛的使用,數據泄漏的危害也越來越嚴重。因此在單位內部對USB存儲設備的操作權限進行控制是很有必要的。

本設計可將不同的USB存儲設備(包括安全存儲設備和普通存儲設備)通過不同的接口接入到主機上,同時對主機和設備問傳輸的數據進行提取,分析和攔截。其應用范圍比較廣泛,為了方便介紹,本文將其作為USB存儲設備管理系統的一部分,根據具體的應用來介紹控制器的設計原理。讀寫控制器可應用在對PC機與安全存儲設備和普通存儲設備的數據共享管理上。其中,PC機的數據要求被保護,安全設備的使用權限被嚴格控制,不會泄漏數據;而普通設備則沒有采取任何安全措施,很有可能向外泄漏數據,比如通用的U盤。

控制器的主要功能是通過不同的接口把兩種USB存儲設備區分開來,實時監測PC機和普通設備間的數據,當檢測到PC機向普通設備寫入數據包時,對其強行破壞,防止數據泄漏。

1 硬件原理

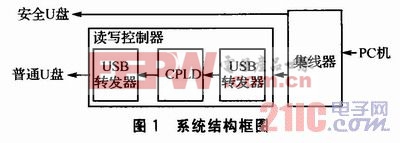

系統的結構框圖如圖1所示。集線器芯片將上游一路USB總線分為兩路:一路直接通過專用的USB接口與安全存儲設備連接,另一路通過讀寫控制器和普通存儲設備連接。讀寫控制器采用CPLD、USB轉發器以及外圍電路實現集線器和普通存儲設備的連接。在CPLD中設計邏輯電路實現對USB轉發器傳輸方向的控制,并對數據進行分析和攔截,以破壞從PC機向普通USB存儲設備傳輸的數據,防止泄漏。

集線器采用的是帶有4個下游端口的GL850G。其端口傳輸的是USB總線的差分信號,故將其上游端口直接接PC機,下游端口接安全USB存儲設備或讀寫控制器。

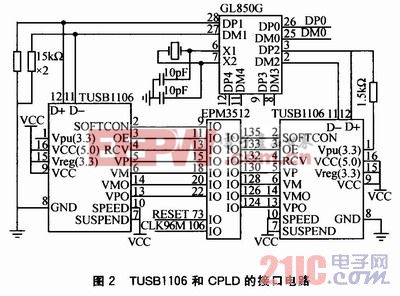

讀寫控制器是由1片CPLD和2片USB轉發器及其外圍電路組成。CPLD采用的是Altera公司的EPM3512。它具有10000個可用的門、512個宏單元、208個可用的I/O引腳,調試和升級簡便,開發十分靈活。市場上關于USB轉接的芯片很多,本文設計的讀寫控制器要求功能簡單、性能穩定,因此USB轉發器采用TI公司的TUSB1106,既滿足設計的要求,也不存在資源浪費。該芯片的詳細介紹見參考文獻。其中VP0、VM0引腳由CPLD驅動。VP、VM和RCV輸人到CPLD中。TUSB1106和CPLD的接口電路如圖2所示。

評論