降低CPLD的功耗的嵌入式應(yīng)用

2.1 設(shè)置偏置電流

通過選擇合適的器件可以控制CPLD的泄漏電流,現(xiàn)在到了運用你的工程技能調(diào)整偏置電流的時候了。用來管理偏置電流的技術(shù)大致分為兩種類型:

確保CPLD的待機配置不與上拉/下拉或相關(guān)的其他器件所用的總線駐留技術(shù)相沖突;動態(tài)控制內(nèi)部功能塊(如振蕩器),使他們只開啟所需要的部分。具體取決于所使用的CPLD,這是增加更多的待機時間到設(shè)計中的好方法。

2.2 并行駐留101方案

在許多設(shè)計中,嵌入式主處理器可以使用自己的總線駐留方案,以保持在總線或I/O上所需的邏輯電平,所以你只須為CPLD的待機模式做準(zhǔn)備,確保其激活總線的管理功能被禁用。在其他應(yīng)用中,總線上其他地方的上拉或下拉電路也可以緩解在待機期間CPLD必須管理總線的情況。

但是,不需要CPLD做任何事情并不意味著你也不需要做任何事情。花些時間驗證只有一個設(shè)備驅(qū)動總線是一個重要的任務(wù),因為單個引腳上的邏輯沖突可導(dǎo)致待機功耗為整個芯片標(biāo)稱值10uA 閑置功耗的2~15倍。

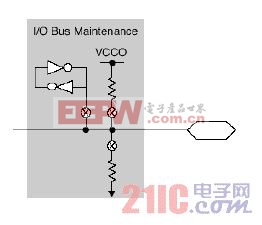

在主總線駐留機制無法使用情況下,可以使用上拉/下拉,以及在大多數(shù)現(xiàn)代的CPLD中擁有的總線保持功能。如同大多數(shù)同類器件,萊迪思的ispMACH 4000ZE CPLD的I/O引腳都配備了可選的上拉和下拉電阻,在待機狀態(tài)(圖3)可提供合適的邏輯電平。4000ZE系列還配備了節(jié)省功耗的總線保持功能(也稱為總線保持):一種弱激活驅(qū)動電路可設(shè)置為激活或零,同時產(chǎn)生比簡單的電阻器消耗小得多的功耗。一點忠告:雖然總線保持功能可大大節(jié)省功耗,但必須肯定它是唯一的在線有源器件,否則會有吸入大電流的風(fēng)險。

圖3 CPLD的總線管理選擇

2.3 動態(tài)功耗管理

設(shè)計人員需要關(guān)注兩種類型的動態(tài)功耗。運行功耗預(yù)算的第一部分是CPLD需要實際工作時的那部分。管理策略的其他部分涉及關(guān)掉輸入至此刻不需要的CPLD的部分,阻止它們切換,或在可能的情況下將它們?nèi)筷P(guān)閉。

2.4 精密的電源管理

雖然CPLD邏輯的許多部分很可能被連續(xù)使用,在有意義的時間段內(nèi)不能禁用,因此使用低電源電壓仍然可以節(jié)省功耗。由于功耗是電壓平方的函數(shù),用1%的精確開關(guān)穩(wěn)壓器,可讓設(shè)計運行于CPLD工作范圍的下限,您可以節(jié)省相當(dāng)多的功耗。例如,如果一個標(biāo)稱值為1.8V的CPLD工作在1.65V,它大約少消耗30%的功耗,這還不包括在較低Vcc的情況下泄漏電流的減少。

評論