基于89C55和FPGA的頻率特性測試儀

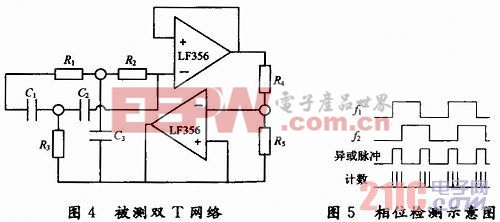

2.3 相位測量

此模塊采用多周期同步計數法。對輸入信號周期進行填充式脈沖計數,具體做法為:利用D觸發器產生一個寬度為整數個被測信號周期的同步閘門信號,將同步閘門信號和時鐘脈沖信號相與后送入計數器1進行記數,計數值為N1;將同步閘門信號、鑒相脈沖和時鐘脈沖三者相與后送入記數器2進行記數,計數值為N2,相位差為φx=(N2/N1)×180。這樣可使量化誤差大大減小,測量精度得到提高,如圖5所示。

閘門的設置、脈沖間的運算、計數等問題在FPGA內部實現可增加系統的靈活性和測量精確度,并可減輕硬件方面的工作量。

3 主要功能電路的設計

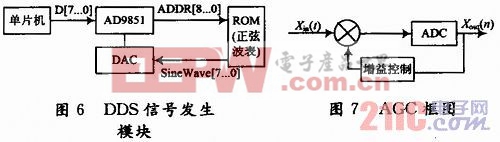

3.1 DDS信號發生模塊

AD9851模塊處理單片機送的頻率控制字,輸出地址值給ROM 1P模塊,ROM 1P模塊中存儲正弦波表,輸出幅度值給DA。具體在FPGA內實現如圖6所示。

3.2 真有效值測量電路

采用典型真有效值一電流轉換芯片AD637,其外圍元件少,頻帶寬。對于有效值為200mV的信號,600 kHz;對于有效值為1 V的信號,-3 dB帶寬是8 MHz,其后接12位高速低功耗串口模/數轉換芯片ADS7818。為簡化電路,并保持電路參數的對稱性,僅采用一個ADS7818,通過電磁繼電器,由單片機控制,在兩路信號間周期性切換進行測幅。

3.3 放大整形及相位測量模塊

由于經過雙T網絡輸出的信號幅度衰減很大,而信號經過過零比較器的傳輸時間為![]() ,式中,G0為過零檢測器的直流增益;fP1是第一個響應極點;f為信號頻率;VP是信號幅值。由該式可以看出,幅度與相移成反比,所以在經過比較器前要加一級放大,采用的是可變增益放大芯片AD603構成的自動增益控制電路,當輸入信號峰一峰值在400 mV~7 V,頻率在6 MHz以下,輸出信號穩定平坦。在此次應用的實際電路中,將有效值從200 mV~3.5 V,頻率從30 Hz~3 MHz的輸入信號無失真的都放大到1.72 V。由于DDS輸出電壓為1.72 V,所以只需放大處理經過網絡后的信號。另外,由于前級為雙T網絡中的射隨,故不需做阻抗匹配。AGC(自動增益控制)電路如圖7所示。

,式中,G0為過零檢測器的直流增益;fP1是第一個響應極點;f為信號頻率;VP是信號幅值。由該式可以看出,幅度與相移成反比,所以在經過比較器前要加一級放大,采用的是可變增益放大芯片AD603構成的自動增益控制電路,當輸入信號峰一峰值在400 mV~7 V,頻率在6 MHz以下,輸出信號穩定平坦。在此次應用的實際電路中,將有效值從200 mV~3.5 V,頻率從30 Hz~3 MHz的輸入信號無失真的都放大到1.72 V。由于DDS輸出電壓為1.72 V,所以只需放大處理經過網絡后的信號。另外,由于前級為雙T網絡中的射隨,故不需做阻抗匹配。AGC(自動增益控制)電路如圖7所示。

輸出信號經過由LM311構成的零點附近的滯回比較器整形后給FPGA,進行相位測量。經過放大整形后的兩路信號先經過一級極性判別電路,通過讀取D觸發器的輸出電平來判斷從雙T網絡輸出的信號相位相對于原信號相位超前還是滯后,VOUT輸出為高電平時超前,反之為滯后。同時將兩個信號送入異或門,得到脈沖信號,測量脈沖信號的寬度,再通過計算就可以得到相位差。當脈沖的寬度很小時,為達到設計要求,標準脈沖的頻率要求很高。設計時使用的是40 MHz的晶振,所以得到相位差的表達式為度。

3.4 示波器顯示模塊

將幅頻相頻信息加至y軸,頻率鋸齒波加至x軸。D/A轉換采用12位串口電壓輸出型可程控偏壓的數/模轉換芯片TLV5638。

評論