基于89C55和FPGA的頻率特性測試儀

2 理論分析與計算

2.1 DDS原理分析

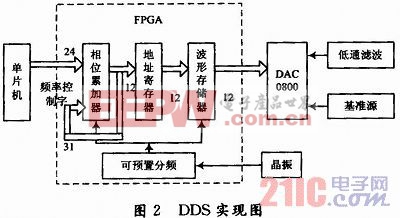

DDS是一種應用數字技術產生信號波形的方法,主要組成:相位累加器、波形存儲器、D/A轉換器和低通濾波器。基本工作原理是:在參考時鐘信號的控制下,通過由頻率控制字K控制的相位累加器輸出相位碼,將存儲于波形存儲器中的波形量化采樣數據值按一定的規律讀出,經D/A轉換和低通濾波后輸出波形。其FPGA內部實現框圖如圖2所示。本文引用地址:http://www.104case.com/article/191062.htm

通過DDS技術實現頻率合成前需要確定DDS的主要性能參數:

設參考頻率源頻率為fclk,采用計數容量為2N的相位累加器(N為相位累加器的位數),頻率控制字為M,則DDS系統輸出信號的頻率為fout=fclk/2N×M,頻率分辨率為△f=fclk/2N。若選取晶振頻率為40 MHz,頻率控制字為24位,相位累加器的位數為31位,此時的DDS模塊邏輯框圖如圖3所示,這樣的理論輸出頻率范圍為0.02 Hz~312 kHz,步進約為0.02 Hz(40 MHz/231)。

2.2 雙T網絡

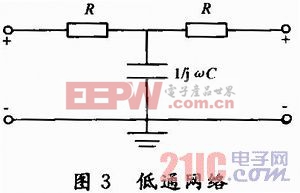

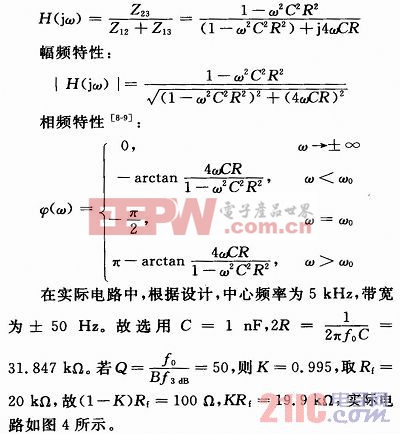

雙T網絡可看作由一個T型低通網絡和一個T型高通網絡組成。低通網絡如圖3所示。將其中的電阻、電容全轉換成阻抗表示。傳遞函數H(jω)為:

評論