基于FPGA的高速串行傳輸系統的設計與實現

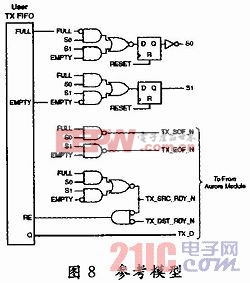

對FIFO時序操作需要根據上述電路圖所產生。在上述電路圖中,有一個D觸發器,其RESET信號是復位信號,復位既是將觸發器輸出端口清零,即將S0置1,將S1置0。在之前的程序中誤將這里寫反,即RESET信號到來之后,將S0置0,S1置1。這樣導致的結果是在最開始輸入的一段數據丟失,之后的結果輸出正常。經過仿真分析之后檢查出問題并已改正。

2.3 AURORA接收模塊

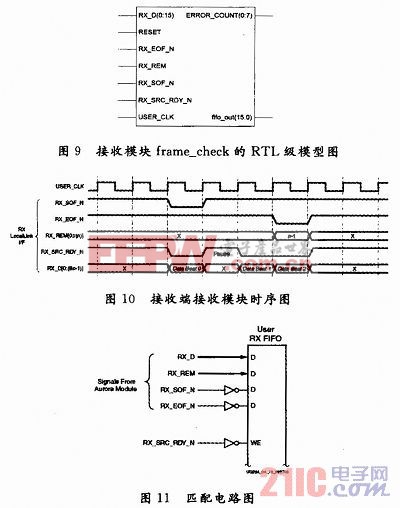

同樣在AURORA協議模塊中,要實現對數據的接收,只需在frame_check模塊中對接收的代碼加以修改,增加自己所需要的內容,完成對數據的解碼提取,剔除冗余信息,并完成數據的緩存。

接收模塊frame_check的RTL級模型圖如圖9所示:其中,RX_D為接收端接收的緩存于FIFO的數據,REsET為復位信號,RX_EOF_N為數據包幀尾的標志,RX_SOF_N為數據包幀頭的標志,TX_SRC_RDY_N為低時代表數據有效,USER_CLK為系統時鐘。fifo_out為數據緩存的輸出,ERROR _COUNT為系統檢錯輸出結果。因此在接收端接收模塊的時序圖如圖10所示。根據該時序圖可以確定接收時序,同樣,在AURORA協議末端,由于與下一級系統的速率可能不匹配,因此需要在接收末端加上一個FIFO做緩存,同樣其電路圖如圖11所示:根據RX_SRC_RDY_N生成FIFO的寫使能信號,該發送模塊設計完畢。

3 測試分析

3.1 功能測試

在基本功能測試中,主要測試光纖模塊傳輸是否正確。由于光纖模塊共有A,B,C,D四個通道,對每個通道都要進行讀/寫測試。將通道A作為數據發送端,通道B作為數據接收端,應用光纖將A,B兩端進行聯通,然后將應用程序數據寫入A通道FIFO中,當FPGA接收到到數據后,將A通道數據通過光纖傳輸到通道B接收緩存中,然后通道B將數據發送到上位機,從而形成一個環路。比較發送和接受端的數據,可以驗證數據傳輸的正確性。同理可以將此方法應用于四個通道中的任意兩個作為發送端和接收端,從而驗證并測試傳輸功能。

3.2 性能測試

性能主要對其傳輸速度和傳輸誤碼率進行測試。就傳輸速度而言,主要由FPGA控制,在其內部設置了兩個初始值為0的計數器,在PCI-Express開始傳輸數據時,FPGA開始計數讀/寫數據包和發送數據包的個數,然后每隔一段時間將計數值寫入兩個計數寄存器中,并將原有值替換,為了精確速率,可以縮短計數時間,并多次測試取平均值,就可得到傳輸瞬時速度。經測試:PCI-Express接口的傳輸速度在600MB/ s,光纖傳輸在850 MB/s,滿足設計要求。對于誤碼率的測試,主要使用誤碼分析軟件對其誤碼性能進行測量,設計由上位機和PCI-Express接口,光纖通道組成數據傳輸環路,通過不同的指令和要求驗證傳輸正確性,當數據包大小在4 Kb,8 Kb,16 Kb,32 Kb,測試數據長度分別為1 000 Kb,1 000 000 Kb,100 000 000 Kb時,錯誤率都為0 b,誤碼率滿足設計要求。

4 結語

該設計系統以Virtex-5為核心構建的平臺,對AURORA協議下串行傳輸系統進行了設計與實現。通過對核心問題的解決,將計算機與外部擴展很好的結合,達到信號傳輸的高速、穩定的目的。實驗證明,板卡設計的整體思路和核心方法的解決是完備的,并使得板卡的傳輸速率和穩定性的到了較大的提高。

評論