基于FPGA的高速串行傳輸系統的設計與實現

由于AURORA光纖通信的輸出時鐘頻率設定的是125 MHz,結合硬件電路的設計,硬件晶振的頻率為20 MHz,因此選擇M值為000011001(25),N的值為10(4),故時鐘芯片的時鐘輸出頻率為:

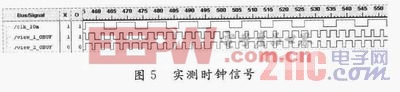

時鐘控制模塊的實測時鐘信號如圖5所示。本文引用地址:http://www.104case.com/article/191038.htm

圖5是用Chipscope在線邏輯分析儀得到的波形,由于Chipscope在線邏輯分析儀的觸發時鐘是100 MHz,因此在抓取125 MHz的時鐘信號時,在圖上顯示的時鐘信號占空比不定,若將時鐘芯片產生的時鐘頻率降低,則此現象消失。

2.2 AURORA發送模塊

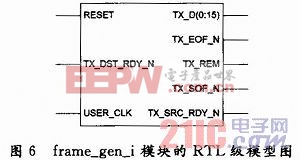

在生成AURORA IP CORE時,同時生成了一個基于AURORA協議的例示程序。因此,要實現基于AURORA協議的光纖通信,在發送端只需要在frame_gen_i模塊將要發送的數據打包,然后通過AURORA模塊發送出去。因此該模塊著重介紹如何將上一級傳送過來的數據進行打包壓縮,形成適合AURORA協議的數據幀,通過AURORA協議發送到接收端。圖6為frame_gen_i模塊的RTL級模型圖。

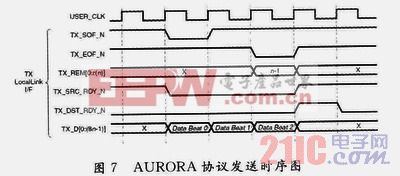

考慮到上一級傳輸數據速率可能會與AURORA傳輸的時鐘頻率不同,因此在發送端建立一個FIFO來做緩沖器。并且AURORA協議的發送時序圖如圖7所示。可以看出,TX_SOF_N為數據包幀的開始標志,TX_EOF_N為數據包幀的結束.標志,TX_REM[0:r(n)]記錄最后的傳輸數據的線程,TX_SRC_RDY_N為低代表數據有效,TX_DST_RDY_N為低代表準備好接受數據,TX_D[0:(8n-1)]是此模塊的輸出數據。以上信息是AURORA協議的發送時序,在使用FIFO做緩沖時也應該遵循這樣的協議。

發送端的FIFO模塊分別包括FIFO的復位信號、FIFO空、FIFO滿、以及讀/寫時鐘、使能和數據信號線。因此應該根據FIFO的標志位empty和full來產生AURORA的發送時序,參考模型如圖8所示:當RESET信號到來之時,首先將S0置為高電平,將S1置為低電平,同時根據FULL和EM-PTY的狀態確定接下來的S0和S1的狀態,進而根據以上邏輯關系得到TX_SOF_N,TX_EOF_N,TX_SRC_RDY_N等邏輯信號,并且根據數據X_DST_ RDY_N和TX_SRC_RDY_N生成FIFO的讀使能。由以上邏輯可以看出,只有在FULL為1,EMPTY為0時,FIFO的讀使能才能被打開。TX_SOF_N為數據包的幀頭標志,TX_EOF_N為數據包的幀尾標志,TX_STC_RDY_N為低時代表數據有效,TX_DST_RDY_N為輸入信號,根據此輸入信號確定FIFO的讀寫時序。

評論