基于FPGA直接序列擴頻系統的設計

摘要 針對一般無線通信系統抗干擾、抗噪聲以及抗多徑性能力差的缺點,提出了一種基于FPGA的直接序列擴頻系統設計。該設計采用63位的pn碼作為擴頻調制的碼序列,在發送端,對信息碼進行擴頻調制;在接收端,對收到的擴頻調制信號進行解擴,增強了系統的抗干擾性和可靠性。同時在Altera公司的QuartusⅡ軟件中,使用硬件描述語言VHDL和原理圖相結合的方法進行了電路的設計實現。通過把電路下裁到Altera公司的CycloneIII的EP3C10E144C8N芯片中調試,驗證了擴頻系統的可行性。

關鍵詞 擴頻;pn碼;FPGA

由于擴頻通信系統具有抗干擾性好、抗多徑衰落能力強,可高精度測量、多址復用等優良特性,多年來得到了迅速發展和廣泛應用。

1 直擴系統基本原理

直接擴頻通信就是在發射端利用高速率擴頻序列去擴展信息數據的頻譜,包括偽碼調制和載波調制這兩個過程。與一般常見的窄帶通信方式不同,主要體現在信息數據經擴展頻譜以后成為寬帶信號,再經過相關處理恢復成窄帶信號后解調出信息數據,因此它具有信號相關處理和偽隨機編碼調制兩大特點。

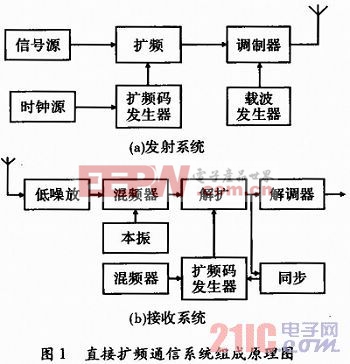

直接擴頻通信系統組成原理如圖1所示,在發端輸入的信息先經信息調制成為數字信號,然后由擴頻碼發生器產生的擴頻碼序列調制數字信號以展寬信號的頻譜。展寬后的信號再調制到射頻發送出去。在接收端將收到的寬帶射頻信號,變頻至中頻,然后由本地產生的與發端相同的擴頻碼序列去相關解擴,再經信息解調、恢復成原始信息輸出。

2 系統總體方案

在發射系統中,首先產生8位的串行信息碼data_in,然后與來自pn碼發生器的擴頻偽碼序列進行模2加,完成信號的頻譜擴展,得到擴頻信號data_kuo。在接收端經過pn碼同步捕獲后,將擴頻調制信號與本地同步擴頻序列進行異或運算,得到解擴信號data_jie,比較data_ kuo與data_jie波形圖,從而驗證系統擴頻解擴的效果與可行性。

3 系統模塊化設計

3. 1 信息碼輸入模塊的產生

該模塊功能是利用8位移位寄存器,在時鐘信號的控制下移位輸出8位信息碼。clr為裝載信號,當clr=0時,從撥碼開關并行讀入8位信息碼,裝入到內部8位寄存器中,當clr=1時,將輸入的8位信息碼在時鐘信號的控制下實現串行移位輸出。

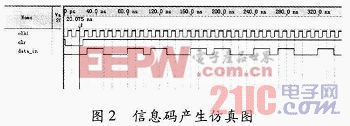

仿真結果如圖2所示,擴頻前的數據信息為11000110B。

評論