基于FPGA的高速串行傳輸系統的設計與實現

ICS8442的性能參數如下:

輸出信號頻率范圍為31.25~700 MHz;晶振頻率范圍為10~25 MHz;VCO頻率范圍為250~700 MHz;

ICS8442是LVDS邏輯電平,具有極低的相位噪聲,這種特性使它非常適合用來為吉比特以太網或同步光纖網提供時鐘信號。

ICS8442的內部結構圖3所示。ICS8442內部有一個完整的PLL鎖相環,其VCO的輸出頻率范圍在250~700 MHz之間,倍頻系數是由M決定的,M的取值范圍在10~28之間。VCO的輸出頻率為:

ICS8442最終的輸出結果還要經過一個分頻器N,最終輸出結果的頻率和晶振輸入頻率的關系式為:

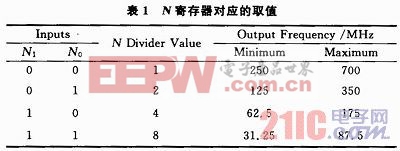

中:N是一個2位的寄存器,其對應的取值如表1所示。本文引用地址:http://www.104case.com/article/191038.htm

對ICS8442時鐘芯片的操作主要是對寄存器M,N的寫操作。ICS8442支持并行寫操作和串行寫操作,根據硬件電路的設計,程序采用串行的寫操作時序。當ICS8442的nP_LOAD置為高電平和S_LOAD置為低電平時,芯片實現串行操作。操作時序如圖4所示。

當S_LOAD置為低且nP_LOAD置為高之后,數據在S_CLOCK的上升沿處寄存在緩沖器中,在S_LOAD的下降沿處將數據鎖存到寄存器M,N中。

評論