ETC中FM0解碼器的設(shè)計

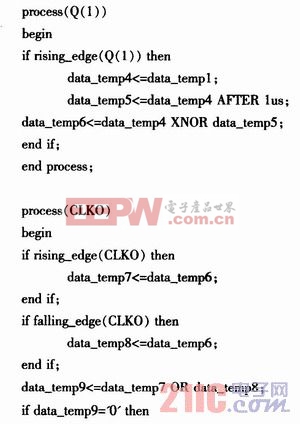

VHDL源代碼如下:

4 結(jié)果仿真

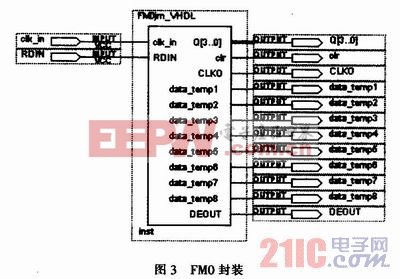

將設(shè)計好的FM0解碼程序進(jìn)行封裝,封裝圖如圖3所示。本文引用地址:http://www.104case.com/article/191004.htm

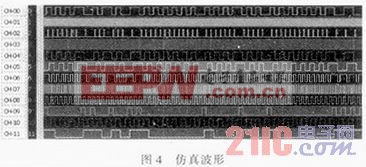

以BST信號為例,解碼數(shù)據(jù)輸入端RDIN輸入BST信號,在解碼時鐘輸入端clk_in輸入16倍數(shù)據(jù)速率時鐘信號(4 096 kB/s)。在QuartusⅡ軟件支持下完成邏輯綜合,將編程數(shù)據(jù)寫入選定的FPGA芯片進(jìn)行測試,可通過邏輯分析儀看到波形。

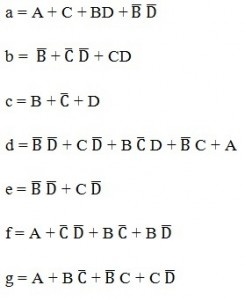

圖4依次給出了RDIN、clk_in、clr、data_temp1、data_temp4、data_temp5、data_temp6、Q1、Q2、Q3、CLKO和DEOUT的仿真波形。從仿真結(jié)果來看,解碼模塊很好地完成了任務(wù),可測得整個解碼過程僅用了8 μs。

同樣的解碼過程用現(xiàn)有的圖形輸入法完成需要40μs,而用VHDL語言編寫只需8 μs,解碼時間是圖形輸入法的五分之一。

5 結(jié)束語

采用高級硬件描述語言VHDL在FPGA上實現(xiàn)FM0解碼設(shè)計,為電子系統(tǒng)的設(shè)計帶來了極大地靈活性。將復(fù)雜的硬件設(shè)計過程轉(zhuǎn)化為在特定的軟件平臺上通過軟件設(shè)計來完成,從而使設(shè)計工作簡化,大大節(jié)約了開發(fā)時間,并大幅度縮短FM0解碼時間。

隨著ETC系統(tǒng)的日益普及,對FM0解碼設(shè)計的需求也大幅提高,因此采用較合適的方法設(shè)計出高性能的FM0解碼器是十分有意義的。

評論