ETC中FM0解碼器的設(shè)計(jì)

3.1 同步時(shí)鐘信號(hào)產(chǎn)生

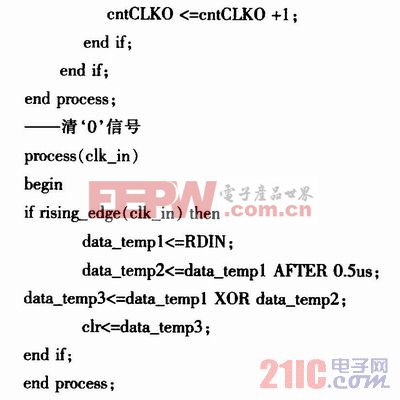

用16倍數(shù)據(jù)速率的時(shí)鐘信號(hào)對(duì)輸入信號(hào)RDIN采樣得到data_temp1信號(hào),將采樣信號(hào)data_temp1延遲一個(gè)16倍時(shí)鐘周期(0.5μs)得到data_temp2信號(hào),data_temp1與data_temp2相異或得到data_temp3信號(hào),如果信號(hào)跳變data_temp3為‘1’,否則為‘0’,得到RDIN跳變時(shí)的脈沖clr信號(hào),當(dāng)clr=‘1’時(shí),清0,當(dāng)clr=‘0’時(shí),對(duì)輸入時(shí)鐘信號(hào)clk_in進(jìn)行2、4、8和16分頻,分別產(chǎn)生同步時(shí)鐘信號(hào)Q0(2 048 kB/s)、Q1(1 024 kB/s)、Q2(512 kB/s)、Q3(256 kB/s)。

16分頻后得到的Q3(256 kB/s)時(shí)鐘信號(hào)不能直接作為解碼輸出的同步信號(hào),clr信號(hào)在輸入信號(hào)跳變時(shí)產(chǎn)生脈沖,盡管輸入信號(hào)RDIN與Q3速率相同,而clr信號(hào)發(fā)生在Q3高電平或低電平處,使Q3受到影響,輸出的不是完整的256 kB/s時(shí)鐘信號(hào)。因此為了得到完整的16分頻時(shí)鐘信號(hào),需將8分頻時(shí)鐘信號(hào)再次2分頻得到時(shí)鐘信號(hào)CLKO。

VHDL源代碼如下:

3.2 在一個(gè)碼元時(shí)間解碼數(shù)據(jù)連續(xù)兩次跳變檢測(cè)

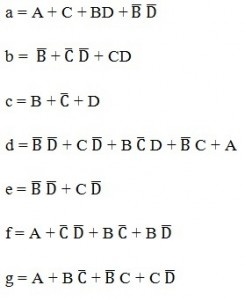

用4分頻信號(hào)Q1對(duì)data_temp1信號(hào)采樣得到data_temp4信號(hào),將采樣信號(hào)data_temp4延遲一個(gè)輸入信號(hào)RDIN的四分之一碼元周期得到data_temp5信號(hào),data_temp4與data_temp5相同或得到data_temp6信號(hào)。用時(shí)鐘信號(hào)CLKO的上升和下降沿同時(shí)檢測(cè)data_temp6信號(hào),求或。如果求或結(jié)果為‘1’則表示時(shí)鐘的上升和下降沿有一次得到‘1’電平,即在半個(gè)碼元的時(shí)間間隔內(nèi)解碼數(shù)據(jù)沒有跳變,根據(jù)FM0編碼規(guī)則此時(shí)數(shù)據(jù)應(yīng)該是‘1’電平,解碼輸出DEOUT輸出為‘1’電平;否則,如果求或結(jié)果為‘0’則表示時(shí)鐘的上升和下降沿均得到‘0’電平,即在半個(gè)碼元的時(shí)間間隔內(nèi)解碼數(shù)據(jù)有跳變,根據(jù)FM0編碼規(guī)則,此時(shí)數(shù)據(jù)應(yīng)該是‘0’電平,解碼輸出DEOUT輸出為‘0’電平。

評(píng)論