正交幅度調制解調器的FPGA設計與仿真

摘要:正交幅度調制技術(QAM)是一種功率和帶寬相對高效的信道調制技術,因此在信道調制技術中得到了廣泛的應用。它的載波信號的FPGA實現一般采用查找表的方法,為了達到高精度要求,需要耗費大量的ROM資源。提出了一種基于流水線CORDIC算法的實現方案,可有效地節省FPGA的硬件資源,提高運算速度,并根據DSP開發工具DSP Builder的優點,采用VHDL文本與Simulink模型圖相結合的方法進行了設計。仿真結果驗證了設計的正確性及可行性。

關鍵詞:正交幅度調制;調制解調器;CORDIC算法;FPGA;DSP Builder

0 引言

正交幅度調制是頻率利用率很高的一種調制技術。與其他調制技術相比,具有能充分利用帶寬、抗噪聲能力強等優點,在移動通信、有線電視傳輸和ADSL中均有廣泛應用。它的載波信號的FPGA實現一般采用DDS(直接數字頻率合成)技術,即在兩塊ROM查找表中分別放置一對正交信號。通過這種方法雖然可以輸出一組完全正交的載波信號,但它主要用于精度要求不是很高的場合,如果精度要求高,查找表就很大,相應的存儲器容量也要很大,使系統的運行速度受到限制,不適合現代通信系統的發展。本文基于CORDIC(Coordinate Rotation Digital Computer)算法,研究正交幅度調制解調器的FPGA實現方法。該方法不僅能夠節省大量的FPGA邏輯資源,而且能很好地兼顧速度、精度、簡單及高效等各個方面。

1 正交幅度調制解調器工作原理

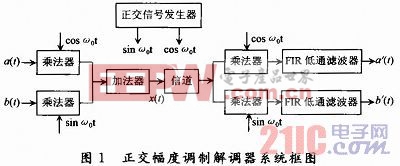

正交幅度調制解調器系統框圖如圖1所示。其中,a(t)和b(t)為兩路相互獨立的待傳送基帶信號,正交信號發生器輸出兩路互為正交的正弦載波信號,經過兩個乘法器可以獲得互為正交的平衡調幅波,即不帶載頻的雙邊帶調幅波。假設乘法器的乘法系數為1,則經過加法器產生的調制信號為:

![]()

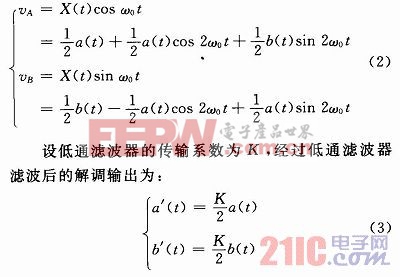

對調制信號X(t)進行解調,采用了正交同步解調方法。已調正交調幅信號X(t)分別與正交信號發生器產生的余弦信號和正弦信號相乘后產生兩路輸出信號:

評論