基于FPGA的多項(xiàng)式運(yùn)算器設(shè)計(jì)

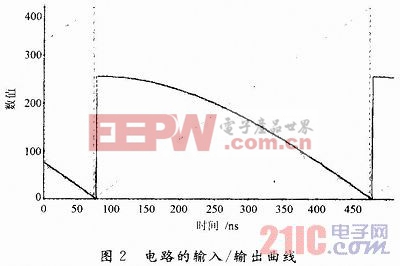

將設(shè)計(jì)下載到芯片XC2VP30,并用Chipscope進(jìn)行片內(nèi)邏輯分析,外部時(shí)鐘和采樣時(shí)鐘都是100 MHz,得到電路的輸入/輸出曲線(見圖2)。圖2中虛線是輸入變量x,實(shí)線是輸出變量y。縱坐標(biāo)的數(shù)值顯示的是Y=y×28的值,即顯示時(shí)沒有考慮小數(shù)點(diǎn)。本文引用地址:http://www.104case.com/article/190462.htm

從圖2中可以看到,輸出有大約3~4個(gè)時(shí)鐘的延時(shí),對(duì)比CPU執(zhí)行1條指令就需要3~4個(gè)時(shí)鐘,運(yùn)算效率已經(jīng)很高,而且這里使用的邏輯資源很少。

4 實(shí)驗(yàn)結(jié)果分析

多項(xiàng)式擬合函數(shù)會(huì)有誤差。這里只分析運(yùn)算器相對(duì)多項(xiàng)式的誤差。因?yàn)閿?shù)據(jù)位寬有限,會(huì)出現(xiàn)截?cái)嗾`差。設(shè)計(jì)實(shí)例采用8位小數(shù)位,最大表示誤差是±2-9。由于常數(shù)也有數(shù)據(jù)截?cái)啵瑢?shí)際運(yùn)算誤差會(huì)更大。

減小誤差的惟一辦法是增加數(shù)據(jù)的位數(shù)。在本例中將數(shù)據(jù)上傳電腦并測(cè)算,最大誤差在x=π/2處,絕對(duì)值是0.0063,相對(duì)值是0.63%。對(duì)于一些特殊的輸入如x=0或x=0.5等,運(yùn)算沒有誤差。

5 結(jié)語(yǔ)

通信系統(tǒng)的仿真與硬件實(shí)現(xiàn)涉及到很多復(fù)雜的函數(shù),直接實(shí)現(xiàn)會(huì)造成資源浪費(fèi),而且實(shí)現(xiàn)難度比較大。采用FPGA實(shí)現(xiàn)多項(xiàng)式運(yùn)算,實(shí)現(xiàn)起來比較簡(jiǎn)單,為之后實(shí)現(xiàn)復(fù)雜函數(shù)提供了基礎(chǔ),大大提高了運(yùn)算速度和實(shí)現(xiàn)效率,在通信系統(tǒng)的硬件實(shí)現(xiàn)上有很廣闊的應(yīng)用前景。

評(píng)論