基于FPGA的多項式運算器設計

摘要:在級數的基礎上,設計一種基于FPGA的多項式運算器。利用該運算器可以在數字系統設計中更好地處理和應用各種函數。首先實現基于FPGA的多項式運算器,利用這個基本單元,進而實現了比較復雜的函數。經過驗證,該運算器結構簡單,運算實時性和準確性都能很好地滿足需要,最后對數據進行了誤差分析。

關鍵詞:多項式;運算器;FPGA;電路設計

0 引言

傳統的DSP都基于CPU結構,是一種基于特定指令系統的處理器,但隨著運算時鐘越來越接近電子器件可以接受的極限,這種DSP的處理能力也在接近它的極限;另一方面隨著EDA技術的發展,尤其像FPGA和CPLD器件的成熟和應用,可以通過直接設計電路來實現并行的運算,這樣運算的效率從本質上得到了提高,而且目前能實時地實現非常復雜的運算,所以基于FPGA的運算器被提上議事日程,并受到越來越多的重視。一種便于用電路實現而且通用性強的算法,可以幫助工程師簡單高效地完成一個能在FPGA上工作的運算器的設計。

1 數字電路實現運算的優缺點

初步的FPGA設計是用硬件描述語言完成器件邏輯功能的描述,一個好的設計必須考慮數字電路的特點。CPU是一個典型的數字電路,因為其只能做加法運算,所以需要通過程序將各種運算都轉換為加法來完成。傳統的“數值分析”正是在這種程序設計的基礎上形成的,不但復雜而且效率不高,不能實現真正的實時運算,而FPGA本身除了能做加法運算外,做無符號數的減法和乘法也很方便。目前兩大FPGA生產商推出的集成開發軟件中,都有集成的加、減法和乘法的IP核,運算效率非常高,對于無符號數的運算一般只要1個時鐘,甚至是不需要時鐘的組合邏輯電路,文獻中也有這些運算器的詳細介紹。但是直接做除法則不同,雖然也有除法IP核,但是需要許多個時鐘,而且占用邏輯資源很多,無論設計還是應用都不方便。電路運算的另一個缺點是表示有符號數和小數,以及做有符號小數間的運算也很麻煩。所以在設計DSP時總是希望能夠找到一種方法盡量的趨易避難。

2 麥克勞林級數和多項式

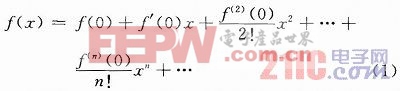

運算器的作用是對數據進行各種運算,這個過程可以用一個函數來表示:y=f(x)。任何一個在零附近連續的函數都可以展開為麥克勞林級數:

大部分常用函數的高階導數項很小或者為零,所以在精度允許的范圍內取其中的有限項就可以,即用一個多項式做近似運算,多項式運算的特點在文獻中有詳細介紹。用FPGA實現多項式的運算,處理很多復雜的函數將會十分方便。

y=a0+a1×x+a2×x2+…+an×xn (2)

本文討論的是一種可以用FPGA或CPLD實現多項式(2)運算的運算器。對于簡單的多項式可以是一個組合邏輯電路,不需要時鐘,所以運算效率很高。這樣許多運算都可以簡單而且高效的完成。

評論