基于FPGA的多項式運算器設計

3.3 設計實例

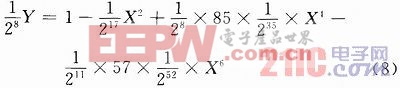

以設計余弦函數(shù)為例,用6次多項式可以很好地擬合(0,π/2)上的余弦函數(shù)。先用麥克勞林級數(shù)計算得到6次擬合多項式:

考慮到三角函數(shù)只有小數(shù)部分有效,所以數(shù)據(jù)只用1個整數(shù)位、另8個小數(shù)位和一個符號位表示。另外需要說明的是常數(shù)保留的小數(shù)位是可以調(diào)節(jié)的,選擇保留合適的常數(shù)小數(shù)位可以盡量在保證精確度的情況下簡化運算。

確定數(shù)據(jù)格式后式(7)可以寫成式(8)的形式,進一步可將式(8)變化為式(9),并在XILINX公司的ISE中完成設計。

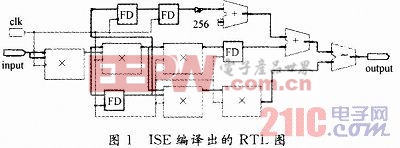

設計中考慮到純粹的異步組合邏輯電路容易出現(xiàn)“競爭-冒險”,所以加入了同步時鐘,這里利用同步時鐘分三步完成運算,同時為了使每一步的運算保持同步還需要加入延時模塊,這樣雖然犧牲了一些時間,但是保證了運行的穩(wěn)定性。圖1是將多項式(9)用ISE編譯出的RTL電路圖,其中“input”為式(9)中的X,“×”為乘法器,“FD”為延時模塊,“output”為式(9)中的Y。本文引用地址:http://www.104case.com/article/190462.htm

評論