基于FPGA高階FIR濾波器的實現

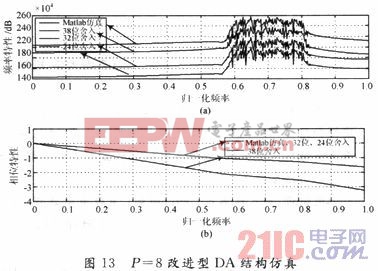

將經過兩種改進型DA算法結構濾波未經截取的38位輸出數據,及經截取的32.24位的輸出數據寫入文本,用Matlab讀取數據并進行幅頻和相頻特性仿真,得到此改進型DA算法結構的濾波器效果一致。圖13為經過改進型DA算法結構濾波后的三組數據幅頻和相頻特性以及Matlab未經量化的幅頻和相頻特性,由圖13可知,經過濾波器后的輸出數據的相頻和幅頻特性明顯優于輸入信號;且輸出的四組數據的幅頻和相頻特性幾乎是相同的,但資源消耗得到了優化。

4 結語

本文詳細介紹了FIR數字濾波器普通DA算法的實現結構,進而提出了改進型DA算法的實現結構。利用Matlab軟件分析了濾波器的精度隨濾波器系數量化位數的變化關系,在濾波器系數的量化位數為16時,濾波器精度和所消耗資源達到最優。并采用Xilinx公司的‘-10’的xc4vsx55芯片,對64階FIR濾波器的兩種改進型DA算法結構進行FPGA仿真,仿真結果表明在高階濾波器方面,改進型DA算法結構在資源消耗、速度以及性能等方面具有較大優勢。最后,利用Matlab軟件對輸出數據以及經過截取的數據進行仿真,得到對濾波器的輸出數據進行適當的截取,不會影響輸出數據的幅頻和相頻特性,但可以提高整個系統的頻率和減少后級的資源消耗。

評論