基于FPGA高階FIR濾波器的實現

3.1 量化位數對濾波器影響

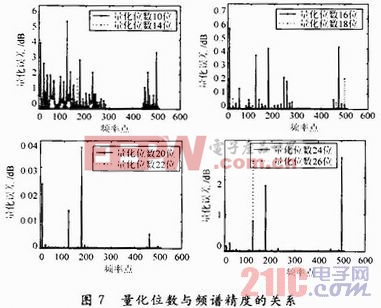

濾波器系數的量化位數與濾波器精度和消耗的硬件資源緊密聯系,利用式(14)計算量化位數對濾波器精度的影響,量化誤差如圖7所示。

err(ω)=(f(ω)-f0(ω))2 (14)

式中:f(ω)為經過量化后的頻譜特性;f0(ω)為標準的頻譜特性。

由圖7可看出,濾波器系數的量化位數越多,濾波器精度越高。當量化位數低于14位時會引入較大的誤差;當量化位數高于16位時,通帶內的量化誤差約為0,阻帶的量化誤差的均值小于0.1能夠滿足設計的需求;當量化位數高于24位時,量化誤差基本不變。綜合頻率精度,資源消耗和查找表的輸出端口為4,設計濾波器系數的量化位數為16位。

3.2 濾波器具體實現

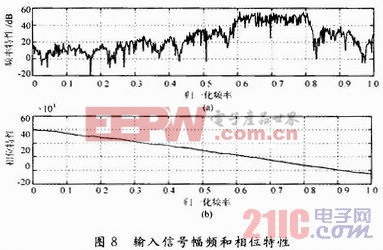

FIR濾波器的輸入信號帶寬為10 MHz,調制頻率為70 MHz,調制系數為0.7的連續相位頻率鍵控(cpfsk)信號,根據中頻采樣定理,采樣頻率為100 MHz,則輸入信號的幅頻和相頻特性如圖8所示。

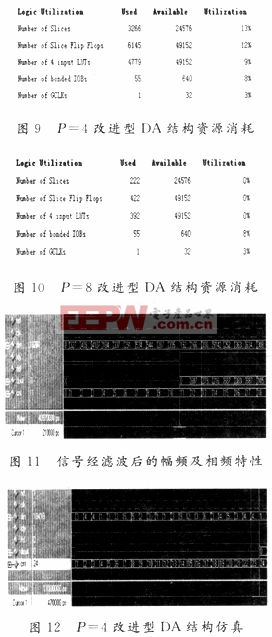

以Xilinx公司‘-10’的xc4vsx55芯片為FIR濾波器的硬件支持,應用Xilinx ISE 9.2i軟件分析存儲器個數P=4的改進型DA算法結構及存儲器個數P=8的改進型DA算法結構設計的濾波器性能,其達到最高速度分別為237.206MHz和264.589 MHz,資源消耗分別如圖9和圖10所示。由圖9和圖10比較可看出,P=4的改進型DA算法結構所消耗的資源比P=8的改進型DA算法結構所消耗的資源高很多。圖11和圖12為兩種改進型DA結構的仿真時序圖,圖中dout代表輸出信號,cnt代表時延計算信號。從圖11及圖12可看出,P=8的改進型DA結構時延為24個時鐘周期(470 ns);P=4的改進型DA算法結構的時延為11個時鐘周期(210 ns)。綜上所述,與P=4的改進型DA算法結構相比,雖然P=8的改進型DA算法結構在時延方面存在不足,但其在資源消耗和速度等方面有明顯優勢。

評論