基于FPGA的全新數字化PCM中頻解調器設計

均勻采樣二階DPLL誤差傳遞函數幅頻特性具有明顯的高通特性,而且通帶截止頻率基本上和環路自由振蕩頻率一致,所以理論上只要恰當地選擇環路自由振蕩頻率就可以得到我們所希望的等效高通濾波器。特別是當通帶截止頻率很小時,高通特性的性能會更好,因為通帶將更加平坦。所以用這種方法實現窄帶高通濾波器要比常規的FIR和HR濾波器都經濟。因此,利用均勻采樣二階DPLL誤差傳遞函效的高通特性濾除緩慢變化的載波頻偏和多譜勒頻率成份,實現等效的開環頻率跟蹤。

2.5 位同步設計

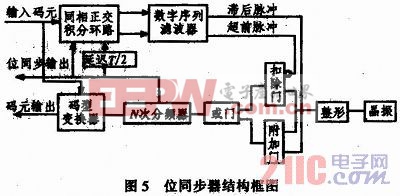

本設計方案中的位同步器主要由同相、正交積分環路、數字序列濾波器、分頻器和碼型變換器幾部分組成。其結構原理如圖5所示,下面將分別說明各個主要組成部分的原理與實現的功能。

同相正交積分環路主要用于實現對接收信號和同步信號的鑒相,利用匹配濾波的原理,比較接收到的信號和晶振產生經過分頻后的信號兩者之間的相位差,輸出超前或滯后脈沖,用于調整位同步脈沖的相位。同相積分器在清除時刻的采樣輸出極性,取決于輸入碼元的極性,而與同步與否以及相位誤差的極性無關。因此,可以將同相積分器的輸出經過保持電路后再進行過零檢測來得到碼元轉換的信息。

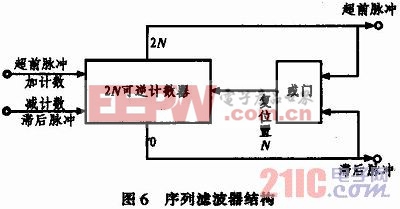

當存在噪聲時,如果超前、滯后脈沖直接用于環路相位調節,將產生相位抖動,特別是在信噪比低或接近予零的情況下,問題更加嚴重。為此,環路中需要使用序列濾波器。這種濾波器專門用于鑒相器輸出的超前或滯后脈沖的情況。它由計數容量為2N的可逆計數器構成,其結構如圖6所示。

可逆計數器對超前脈沖進行向上計數,對滯后脈沖進行向下計數。在開始計數時,可逆計數器的狀態為N,當超前脈沖比滯后脈沖多N個時,可逆計數器計滿到容量2N,同時輸出一個推后控制脈沖,以便用它去控制本地估算信號的相位推后一步。與此同時,或門就輸出一個脈沖,將可逆計數量N,重新開始計數。而當滯后脈沖比超前脈沖多N個時,可逆計數器的計數值為0,同時輸出一個提前控制脈沖,以便用它去控制本地估算信號的相位前移一步。這時,或門也輸出一個脈沖,將可逆計數置N,重新開始計數。

評論