基于FPGA的光纖通信系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)

NRZI編碼器ModelSim仿真波形如圖8所示。data_in輸入數(shù)據(jù)分別為D30.0和D7.1。本文引用地址:http://www.104case.com/article/190204.htm

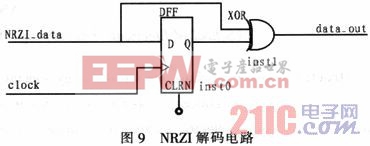

4.2 NRZI解碼器設(shè)計(jì)

NRZI解碼器設(shè)計(jì)是NRZI編碼器的逆過(guò)程。圖9為本設(shè)計(jì)采用的NRZI解碼電路。其中,DFF為D觸發(fā)器,XOR為異或門(mén)。NRZI_data為信號(hào)輸入端,數(shù)據(jù)來(lái)自經(jīng)光纖傳輸?shù)腘RZI碼;clock時(shí)鐘頻率同編碼起時(shí)鐘頻率,即為NRZI_data碼元速率的2倍(由FPGA倍頻電路實(shí)現(xiàn));data_out為解碼器輸出。

NRZI解碼器ModelSim仿真波形如圖10所示。NRZI_data輸入數(shù)據(jù)分別為D30.0和D7.1編碼后的數(shù)據(jù)。

5 結(jié)束語(yǔ)

文中主要用Verilog語(yǔ)言編寫(xiě)了位同步時(shí)鐘提取模塊、8B/10B編解碼模塊、NRZI編解碼模塊等來(lái)實(shí)現(xiàn)光纖通信。8B/10B編碼很好地平衡了位流中0和1的個(gè)數(shù),特別適合光纖介質(zhì)的信息傳輸;NRZI編碼使信號(hào)的狀態(tài)變化更加頻繁,進(jìn)一步增強(qiáng)了發(fā)送設(shè)備與接收設(shè)備的可同步性;位同步時(shí)鐘提取使得發(fā)送設(shè)備與接收設(shè)備保持同步,同時(shí)為接收端解碼器提供可靠的時(shí)鐘參考。這幾大模塊相輔相成,共同維持光纖通信系統(tǒng)可靠、高效的運(yùn)行。

評(píng)論