基于FPGA的光纖通信系統(tǒng)的設(shè)計與實現(xiàn)

3.2 編碼器設(shè)計

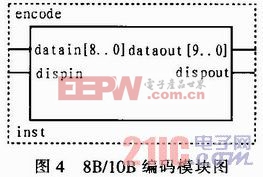

從編碼的種類看,直流平衡8B/10B編碼可分為數(shù)據(jù)字符編碼和控制字符編碼兩種,但是從編碼的組成看,它又可分為3B/4B編碼、5B/6B編碼兩部分。根據(jù)圖3 8B/10B編碼模塊圖將編碼器設(shè)計劃分為3個模塊:3B/4B編碼模塊、5B/6B編碼模塊和Dispartity運算模塊。基于Verilog語言的8B/10B編碼模塊圖,如圖4所示。本文引用地址:http://www.104case.com/article/190204.htm

datain[8:0]為編碼數(shù)據(jù)輸入引腳。datain[4:0]為5位5B/6B編碼數(shù)據(jù)輸入端,即為ABCDE,其中E為最高位,分別用ai、bi、ci、di和ei表示每一位。datain[7:5]為3位3B/4B編碼數(shù)據(jù)輸入端,即FGH,其中H為最高位,分別用fi、gi和hi表示每一位。datain[8]為控制字符編碼標示位,用ki表示,ki為1表示為控制字符編碼,為0表示為數(shù)據(jù)字符編碼。dispin為8B/10B編碼前的RD輸入引腳;dispout為8B/10B編碼后的RD輸出引腳。dataout[9:0]為編碼數(shù)據(jù)輸出引腳。dataout[5:0]為8B/10B編碼后5B/6B編碼模塊對應(yīng)輸出引腳。dataout[6:9]為

8B/10B編碼后3B/4B編碼模塊對應(yīng)輸出引腳。

8B10B編碼器ModelSim仿真波形如圖5所示。其中datain、dispin、dispout和dataout分別為圖4編碼模塊圖對應(yīng)的信號。仿真時選取了D31.2(RD+)、D31.0(RD-)、D28.0(RD+)和K28.0(RD+)作為仿真輸入信號。

4 NRZI編/解碼的FPGA實現(xiàn)

NRZI(Non-Return to Zero Inverted不歸零反轉(zhuǎn))編碼是在數(shù)據(jù)位1時發(fā)生跳變,為0時保持不變的一種編碼。在光線通信中,由于光纖固有的特性,信號長時間的置0或置1容易造成數(shù)據(jù)傳輸錯誤,應(yīng)當盡量避免這種情況發(fā)生,NRZI編碼能夠很好地解決這一問題。前面的8B/10B編碼已經(jīng)在很大程度上緩解了這個問題,但為了進一步提高數(shù)據(jù)傳輸質(zhì)量,在8B/10B編碼的基礎(chǔ)上加入一級NRZI編碼。

4.1 NISEI編碼器設(shè)計

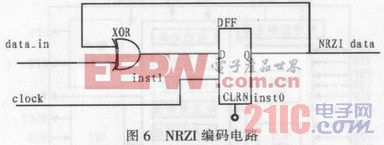

NRZI的編碼規(guī)則是:數(shù)據(jù)位為1時發(fā)生跳變,為0時保持當前狀態(tài)。圖6為本設(shè)計采用的NRZI編碼電路。其中,DFF為D觸發(fā)器,XOR為異或門;data_in為數(shù)據(jù)信號輸入端,數(shù)據(jù)來自編碼后的8B/10B碼;clock為NRZI編碼時鐘,clock時鐘頻率為data_in碼元速率的2倍頻(由FPGA倍頻電路實現(xiàn));NRZI_data為NRZI編碼器輸出。

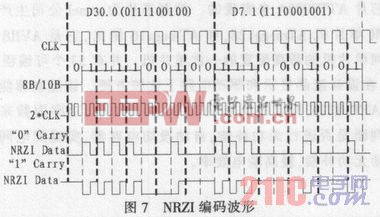

下面以一具體實例說明NRZI的編碼過程。8B/10B碼D30.0(011110 0100)和D7.1(111000 0100)編碼后的波形圖如圖7所示。經(jīng)NRZI編碼后信號狀態(tài)變化更加頻繁,這些狀態(tài)變化使得接收器能夠持續(xù)地與輸入信號向相適應(yīng),這樣就保證了發(fā)送設(shè)備和接收設(shè)備之間的同步。由于8B/10B碼的有效編碼中都至少有4位“1”,從而保證了傳輸?shù)男盘栔辽侔l(fā)生4此跳變,以利于接收端的時鐘提取。

評論