基于FPGA的光纖通信系統的設計與實現

摘要:光纖通信是現今數據通信系統的主要通信方式,其性能的好壞直接影響數據通信系統的質量。本文采用Verilog語言實現FPGA光纖通信系統的功能。光纖通信系統又包含位同步時鐘提取模塊、8B/10B編解碼器模塊和NRZI編解器模塊;這些模塊都利用了DA(Design Analyz er)、Quartus II以及Modelsim等EDA工具來完成綜合與仿真,從仿真的結果可以看出該設計方法很好地滿足了系統的要求。

關鍵詞:光纖通信;FPGA;位同步時鐘;Verilog

光纖收發器與FPGA技術相結合的方案是現在光纖通信系統的主流解決方案。目前,在超高速光纖通信中還多采用專用的ASIC芯片,但最近各FPGA廠商也相繼推出了40Gbps、4x10Gbps、100Gbps和10x10Gbps等FPGA芯片,使基于FPGA超高速光纖通信的實現成為可能。FPGA的可編程特性,具有ASIC芯片無法比擬的優越性。所以基于FPGA的光纖通信有很大的現實意義。

1 光纖通信系統結構設計

光纖通信系統主要由位同步時鐘提取模塊、8B/10B編解碼器模塊和NRZI編解器模塊組成.主要功能框圖如圖1所示。數據經8B/10編碼后,能在很大程度上平衡位流中0與1的個數,而NRZI編碼又做了進一步的平衡,主要是為了使信號狀態變化趨于頻繁以便位同步時鐘提取模塊更好、更快的提取出位同步時鐘。編碼后的信號為LVTTL電平信號,先經電平轉換模塊轉換為PECL電平信號,再由光發送接收模塊轉換為光信號送入光纖傳輸介質。經光纖傳輸后,在接收端先經光發送接收模塊把光信號轉換為PECL電平信號,再由電平轉換模塊把PECL電平信號轉換為LVTTL電平信號,同時位同步時鐘提取模塊提取出同步時鐘,為解碼模塊提供參考時鐘。最后,接收到的數據經解碼后數據輸出。

2 位同步時鐘提取的FPGA實現

在數字通信系統中,任何消息都是通過一連串的碼元序列傳送的,所以接收時需要知道每個碼元的起止時刻,以便在恰當的時候取樣判決。這就要求接收端必須提供一個位定時脈沖序列,該序列的重復頻率與碼元速率相同,相位與最佳取樣判決時刻一致。這種提取定時脈沖序列的過程稱為位同步。同步性能的好壞直接影響通信系統的性能,出現同步誤差或失去同步就會導致通信系統性能下降或通信中斷。

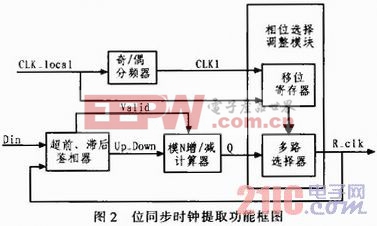

提取位同步信號有多種方法,其中最常用的是數字鎖相法。其基本原理是:在接收端利用鑒相器比較接收碼元和本地產生的位同步信號的相位,若兩者相位不一致(超前或滯后),鑒相器就產生誤差信號去調整位同步信號的相位,直至獲得準確的位同步信號為止。本設計采用數字鎖相法提取位同步時鐘,主要由鑒相器、分頻器和相位選擇調整模塊等幾大部分組成。其功能框圖如圖2所示。

評論