基于FPGA的光纖通信系統(tǒng)的設(shè)計與實現(xiàn)

CLK_local是利用FPGA內(nèi)部的鎖相環(huán)倍頻后得到的高穩(wěn)定度、高頻時鐘。CLK1是CLK_local經(jīng)N次分頻后得到的,分頻系數(shù)N要求滿足分頻后的時鐘CLK1等于所要提取出的位同步時鐘R_clk。Din為接收到的碼元。Valid為超前、滯后鑒相器的使能輸出,Up_Down為超前、滯后鑒相器的比較輸出,Valid為邏輯0時關(guān)閉模增/減計數(shù)器,Valid為邏輯1時開啟模增/減計數(shù)器,如果位同步時鐘滯后時Up_Down的輸出為邏輯0,使模增/減計數(shù)器進行減計數(shù),如果位同步時鐘超前時Up_Down的輸出為值為邏輯1,使模增/減計數(shù)器進行增計數(shù)。

接收到的碼元經(jīng)超前、滯后鑒相器后,如果位同步時鐘滯后則計數(shù)器減計數(shù),從而通過多路選擇器后減少一個單位的延遲,反之如果位同步時鐘超前則計數(shù)器進行增計數(shù),從而通過多路選擇器后增加一個單位的延遲。

3 直流平衡8B/10B編/解碼的FPGA實現(xiàn)

8B/10B編碼(以下簡稱8B/10B)作為一種高性能的串行數(shù)據(jù)編碼標準,其基本思想就是將一個字節(jié)寬度的數(shù)據(jù)經(jīng)過映射機制(Mapping Rule)轉(zhuǎn)化為10為寬度的字符,但是平衡了位流中0與1的個數(shù),也就是所謂的直流平衡特性。同時規(guī)定位流中0或1的游程長度(Run Length)的最大值不能大于5,以使得傳輸過程保持足夠高的信號變換頻率,這樣不僅確保了時鐘恢復(fù)也使得信息流的直流頻譜分量為零或近乎為零,而正是這些特性使得8B/10B編碼特別適合光纖等介質(zhì)的連接和信息傳輸。

3.1 直流平衡8B/10B編碼

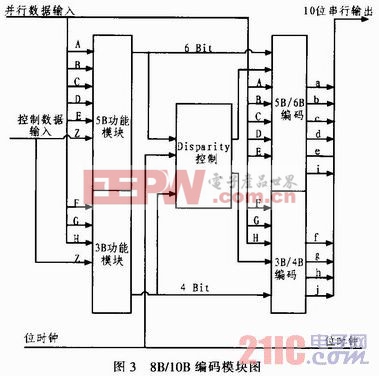

如圖3所示,通信適配接口的輸入由一個字節(jié)的數(shù)據(jù)(ABCDEFGH)、一個控制信號(Z)以及一個時鐘信號組成,其中時鐘采樣以字節(jié)為單位。控制信號Z是數(shù)據(jù)信號或控制信號的標示位。輸入數(shù)據(jù)ABCDEFGH被分成兩部分,其中ABCDE經(jīng)5B/6B編碼生成6比特字符abcdei,而FGH經(jīng)3B/4B編碼得到fghi,最后組合輸出得到10比特的傳輸字符abcdeifghi。本文引用地址:http://www.104case.com/article/190204.htm

評論