基于FPGA的IRIG-B(DC)碼解碼

秒信息從00~59,分為“秒”和“十秒”兩部分,分別使用BCD碼表示。“秒”使用1,2,3,4碼元,“十秒”使用6,7,8碼元。分信息也是從00~59,分為“分”和“十分”,“分”使用10,11,12,13碼元,“十分”使用15,16,17碼元。小時信息從00~23,分為“時”和“十時”,“時”使用20,21,22,23碼元,“十時”使用25,26碼元。天表示的是從1月1日到當前日期的總天數,如1月1日,天數為1。天數從1~365(閏年為366),分為“天”,“十天”和“百天”三部分,“天”使用30,31,32,33碼元,“十天”使用35,36,37,38碼元,“百天”使用40,41碼元,TOD時間使用80,81,82,83,84,85,86,87,88,90,91,92,93,94,95,96,97共17個碼元,采用直接二進制表示從每天的第一秒到當前時刻的總秒數。23點59分59秒對應的TOD時間為86 399 s的IRIG-B(DC)碼如圖2所示。注意,秒、分、時、天、TOD表示都是低位在前,高位在后;第5、14、24、34碼元為索引標志碼元。另外,標志位P5到P8之間的碼元為控制碼元,可以根據實際使用時的協議來制訂使用方法。

2 FPGA解碼方案

FPGA是現場可編程門陣列(Field ProgrammableGate Array)的簡稱。FPGA器件及其開發系統是開發大規模數字集成電路的新技術。在電子產品設計中有較廣泛的應用。在本設計中采用的是Xilinx公司Spartan3系列中的XC3S1500芯片。它具有29952個邏輯單元,150萬個門。XC 3S1500具有333個管腳,采用FG456封裝,支持在線可編程。

Xilinx公司提供了支持FPGA開發的軟件ISE,通過它可以進行原理圖編輯,VHDL文本語言編輯,并支持這兩種編輯方式的混合設計。在本設計中采用的是ISE 10.1軟件。完成了設計輸入并成功地進行了編譯,只能說明設計符合一定的語法規范,并不能保證設計可以獲得所期望的功能,這時就需要通過仿真對設計進行驗證。ModelSim是業界十分優秀的語言仿真器,它提供十分友好的調試環境,仿真速度快,精度高。在本設計中采用的是ModelSim SE 6.6e。

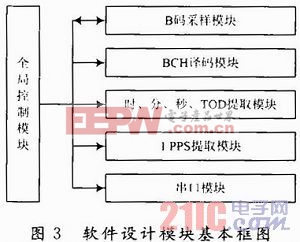

在本工程設計中采用了VHDL語言,自頂向下的設計方法,實現了工程的層次化管理。為了使得產品穩定、可靠,采用全同步設計,使整個工程都在一個時鐘上升沿時刻改變狀態。這樣可以避免冒險和其他不定態的出現。其軟件設計模塊基本框圖如圖3所示。本文引用地址:http://www.104case.com/article/190174.htm

評論