基于FPGA的IRIG-B(DC)碼解碼

摘要:在分析了IRIG-B(DC)碼碼型特點的基礎上,提出了一種IRIG-B(DC)時間碼解碼的設計方法。該方法由少量外圍電路與一片現場可編程門陣列(FPGA)芯片組成,來實現對IRG-B(DC)碼的解碼、1 PPS信號輸出、實時時間顯示以及串行異步通信。與傳統的方法相比,該設計方案具有體積小、成本低、工作穩定等優點,完全能夠替代傳統的B碼機箱的功能。

關鍵詞:IRIG-B(DC);FPGA;硬件描述語言;串行通信

隨著電力自動化水平的提高,電力對時間的同步要求越來越迫切、時間同步的精度要求越來越高。采用GPS全球衛星定位系統的時間同步功能,是提高電力生產和管理自動化水平、確保運行質量的一條最佳途徑。國家電力公司、各大電網和省電力公司,高度重視電力系統的時間同步系統的建設,明確要求電力的生產運行系統裝置采用衛星時鐘進行校時。由于目前GPS接收機采用IRIG-B(DC)時間碼的格式輸出標準時間信息,所以本文提出了一種基于FPGA來實現的IRIG-B(DC)時間碼解碼設計方案。

1 IRIG-B碼簡介

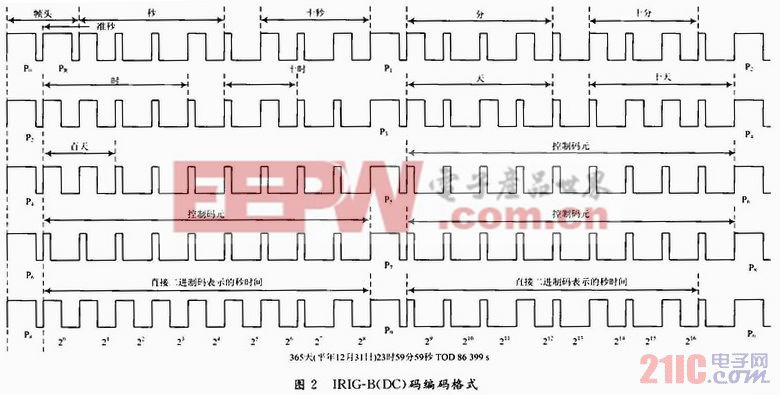

IRIG-B(DC)時間碼(簡稱B碼)是由IRIG所屬的TCG(Telecommunication Group)制訂的一種串行時間碼。B碼是一種串行時間碼,幀長為1 s,共包含100個碼元。它采用脈寬調制方式編碼,共有三種寬度的碼元,分別表示“0”,“1”.“P”,其中“P”為標志位,如圖1所示,碼元的總寬度為10 ms,“0”的脈寬為2 ms;“1”的脈寬為5 ms;“P”的脈寬為8 ms。

B碼的1幀從連續兩個“P”開始,其中第一個標志位為P0,第二個標志位為PR,PR的上升沿是1 s的準秒時刻,即當前幀表示的秒時刻的起點。如果規定PR所在位置為第0個碼元,那么每幀分別有編號為0,1,2,…,99的碼元。標志位P1,P2,P3,…,P0的位置分別在9,19,29,…,99。B碼包含了當前時刻的秒,分,時,天信息和每天按秒計時的秒數(TIME OF DAY,TOD),如圖2所示。

評論