采用歐氏算法和頻譜結構分析相結合的RS硬件解碼方

3.2 利用伴隨式確定關鍵方式 本文引用地址:http://www.104case.com/article/190170.htm

Euclidean算法的難點主工在于迭代計算過程中存在的被除數多項式和除數多項式長度的不確定性,使每次計算中產生的商序列的長度不等,以及因此可能涉及到的不定長多項式的相乘和相加問題,增加了硬件設計的難度。系統采用了嵌套雙循環的方法,利用'時鐘產生2'控制外循,'時鐘產生1'控制內循環,從而優化了算法,得到了問題的解決方案。在獲得伴隨式的基礎上,圖3電路可具體完成Euclidean算法對關鍵方程的求解 σ(x)=σtxt+σt-1xt-1+…+σ1x+1。

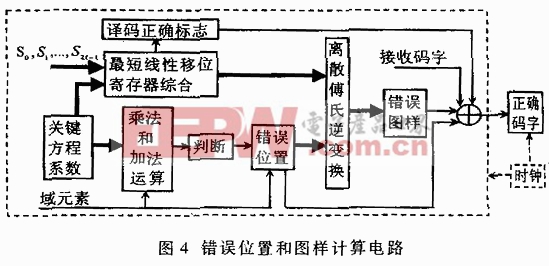

3.3 利用最短線性移位寄存器綜合和離散傅氏變換獲取錯誤圖樣

在得到關鍵方程后,首先應進行錯誤位置(關鍵方程的根)的確定,這樣可減小電路的規模;利用錢搜索[1](工程上求解σ(x)根的實用方法)的方法可以簡捷的確定錯誤位置。然后,啟動最短線性移位寄存器綜合和離散傅氏逆變換,經過N次(運算所在域的長度)迭代,即可求得對應各個錯誤位置的錯誤圖樣,如圖4所示。用錯誤圖樣對接收碼字進行糾錯,就可得到正確的信息序列。

3.4 RS編譯碼在FPGA上的實現

有限域的乘法、加法運算單元和各模塊的控制邏輯設計是系統成功的關鍵。涉及有限域的各個運算單元的運算速度制約了譯碼器的速度,而控制邏輯引導了譯碼的流程。硬件電路的軟件開發工具給設計復雜電路提供了簡捷思路。系統采用了QUARTUS與第三方軟件相結合的方法,用VHDL語言設計了大部分功能模塊。特別是在乘法器設計中,乘數確定、被乘數不定的有限域乘法器,經邏輯綜合和優化設計后,運算速度可分別在6.8ns和11.6ns內完成,完全可以滿足系統符號速率50Mbps的要求。應該指出,系統速度的進一步提高受到求逆運算的限制,求逆運算沒有明確的數學結構(通常采用查表的方法),這是制約運算速度的瓶頸。但針對流式譯碼算法,上述結構已能滿足要求。

4 仿真結果

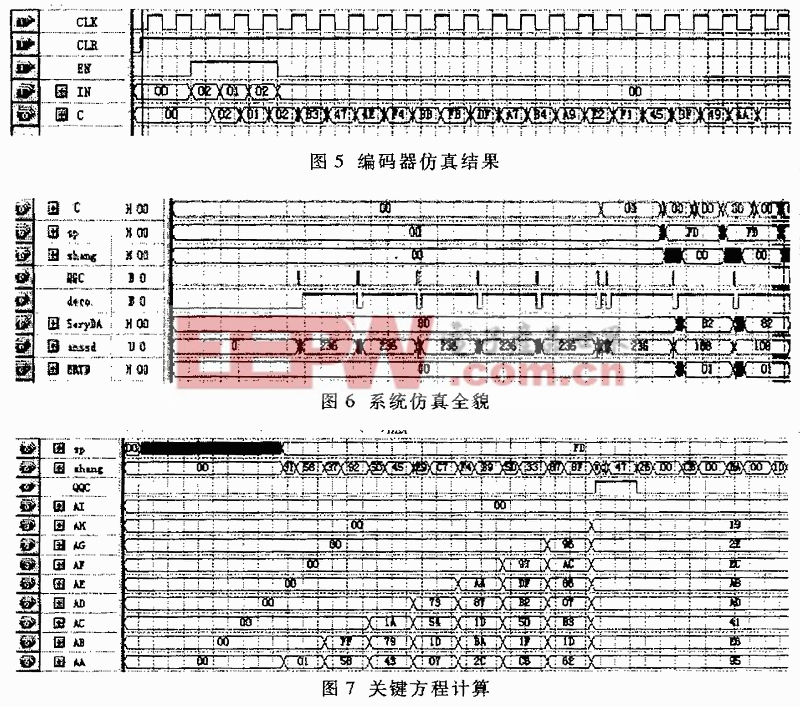

4.1 編碼器的仿真

仿真的時鐘頻率為50MHz,在EN為高電平時輸入信息有效。為簡單起見,采用系統碼的縮短型,即信息為(00,00,…,00,02,01,02).編碼器的仿真結果如圖5所示。其中,IN為輸入信息, CLK為系統時鐘,C為編碼輸出(輸入和輸出均為16進制)。

4.2 譯碼器的仿真

首先,給出系統的仿真全貌,如圖6所示。其中C為接收到的RS碼,SP為伴隨式 S15,shang為運用歐氏算法得到的商序列,SeryDA為S序列,anssd和ERTD分別對應碼字可能存在的第四個錯誤位置和錯誤值,仿真中的接收碼在位置(105,106,107,108,109,110,111,112)上錯誤均為(01)HEX。

伴隨式的計算結果:S15,S14,…,S1,S0為(FD,8D),CE,4A,51,B2,A1,CA,C4,0D,73,56,A6,F5,01),圖6和圖7中的sp即為S15。

這里重點給出利用伴隨式計算關鍵方程的電路仿真結果,如圖7所示。當輸入伴隨式結果以后,運算電路啟動,在計算商序列的同時進行聯接多項式的迭代運算。歐氏算法的商序列shang為:(FF,58),(37,92),(50,45),(E9,C7),(F4,B9),(5D,33),(87,8F)。當滿足終止條件以后顯示標志QQC,同時,給出關鍵方程系數如圖7中(AI,AH,AG,AF,AE,AD,AC,AB,AA)即(00,19,2E,EC,A8,AD,41,E6,95),對應有限域上的表達式為:

δ(x)=α193x7+α130x6+α122x5+α144x4+α252x3+α191x2+α160x+α184; 有解為(α105,α106,α107,α108,α109,α110,α111),與假定錯誤位置完全一致。然后求解S序列,同時針對各錯誤位置進行 IDFT,就可以得到對應的錯誤值。圖6中anssd和ERTD表示位置108上存在的錯誤為(01)HEX。

系統仿真表明,譯碼器獲得的錯誤位置和錯誤圖案與實際假設的錯誤位置(105,106,107,108,109,110,111)和錯誤值(01)HEX完全一致。

基于APEX架構的可編程單芯片RS編譯碼硬件解決方案在中國普天集團西安藍牙通訊設備有限公司的二次群無線擴頻通信機的改造項目中得到了應用。它可用于離散譯碼、流式譯碼,在添加一級緩存的基礎上,同樣適用于連續譯碼。

評論